To those I love and those who love me

"Education does not end at any point in our lives; it is an ongoing journey to be carried with us everyday throughout our lives." Thomas Powell

## Synopsis

The pioneering works of Prof. Leon O. Chua constructing electrical circuit (named *Chua's circuit*) which can display chaotic behaviors open a period with fruitful researches about nonlinear circuits. A considerable amount of different nonlinear circuits has been introduced and their numerous applications have developed instantaneously. Complex dynamical characteristics of nonlinear circuits are used to model complex systems, to generate random numbers or to secure informations. There are three nonlinear systems which have received much attention recently: time—delay system, Cellular Neural Network and memristive system. In this thesis we investigate how the properties of these nonlinear systems can be efficiently exploited to build novel chaotic systems and to observe novel complex phenomena.

## Acknowledgement

"You raise me up, so I can stand on mountains;

You raise me up, to walk on stormy seas;

I am strong, when I am on your shoulders;

You raise me up... To more than I can be."

(Brendan Graham/Rolf Lovland, 2002)

It is my great pleasure to have this opportunity for showing my appreciation to all people who supported me during my PhD course in University of Catania.

Foremost, deep gratitude goes to my supervisor Prof. Luigi Fortuna, without him, I could not have come and studied here. I wish to express my thanks to him for his invaluable supports, supervisions, giving me guidance and valuable advice. Without any of these, it would not have been possible to complete this PhD thesis.

I would like to show special thanks my co-supervisor Prof. Mattia Frasca. His constructive feedbacks, comments and suggestions at ev-

#### X Acknowledgement

ery stages encouraged me to pursue and complete interesting challenge topics.

I also want to thank Prof. Thang Manh Hoang who gives me prestigious suggestions during my visiting period at SIPLab, HUST.

I would like to thank all members of Automatic Control Laboratory, DIEEI, University of Catania. I have learned a lot from them through the memorial three—year period. The warm and continuous support they have given me since I came to Catania is the thing I will not forget. I am really appreciated for what they have done for me.

Finally, but not mean the least, I would like to thank members in my family for their attention and loving care.

## Contents

| 1 | Introduction                                                 | 1  |  |  |  |

|---|--------------------------------------------------------------|----|--|--|--|

|   | 1.1 Problem statements                                       | 1  |  |  |  |

|   | 1.2 Objectives                                               | 3  |  |  |  |

|   | 1.3 Contributions and contents                               | 4  |  |  |  |

| 2 | Design of time-delay chaotic electronic circuits             | 7  |  |  |  |

|   | 2.1 Introduction                                             | 7  |  |  |  |

|   | 2.2 Nonlinear block                                          | 9  |  |  |  |

|   | 2.3 Time–delay block                                         | 13 |  |  |  |

|   | 2.4 Design procedure for time–delay chaotic system           | 18 |  |  |  |

| 3 | Implementation of chaotic circuits with a digital            |    |  |  |  |

|   | time-delay block                                             |    |  |  |  |

|   | 3.1 Design of chaotic circuits with digital time–delay block | 26 |  |  |  |

|   | 3.2 FPGA-based implementation                                | 29 |  |  |  |

|   | 3.2.1 Implementation of the time–delay                       | 29 |  |  |  |

|   | 3.2.2 Implementation of the chaotic circuit                  | 33 |  |  |  |

|   | 3.3 Accuracy of the implementation                           | 37 |  |  |  |

| 4 | Me  | emristive Cellular Neural/Nonlinear Networks               | 43 |

|---|-----|------------------------------------------------------------|----|

|   | 4.1 | Autowaves in Cellular Neural Network                       | 44 |

|   |     | 4.1.1 Model of the memristive CNN                          | 45 |

|   |     | 4.1.2 Simulation results                                   | 51 |

|   | 4.2 | FPGA-based generation of autowaves in Memristive           |    |

|   |     | Cellular Neural Networks                                   | 53 |

|   |     | 4.2.1 FPGA-based implementation of Memristive              |    |

|   |     | Cellular Neural Networks                                   | 56 |

|   |     | 4.2.2 Experimental results                                 | 60 |

| 5 | Sin | aple memristive time-delay chaotic systems                 | 65 |

|   | 5.1 | Models of memristive time–delay systems                    | 67 |

|   |     | 5.1.1 The 6–element memristive time–delay system           | 67 |

|   |     | 5.1.2 The 2–element memristive time–delay system           | 69 |

|   |     | 5.1.3 One–element memristive time–delay system             | 72 |

|   | 5.2 | Implementation of the 2–element memristive time–delay      |    |

|   |     | system                                                     | 75 |

|   | 5.3 | Implementation of the single–memristor–based chaotic       |    |

|   |     | circuit                                                    | 81 |

| 6 | No  | ise in chaotic circuits                                    | 87 |

|   | 6.1 | Chaos control in a system with only one stable             |    |

|   |     | equilibrium and in the presence of noise                   | 87 |

|   |     | 6.1.1 Chaotic system with only one stable equilibrium $$ . | 89 |

|   |     | 6.1.2 Feedback control                                     | 90 |

|   |     | 6.1.3 Experimental results                                 | 93 |

|    |       |                                                 | Contents  | XIII |

|----|-------|-------------------------------------------------|-----------|------|

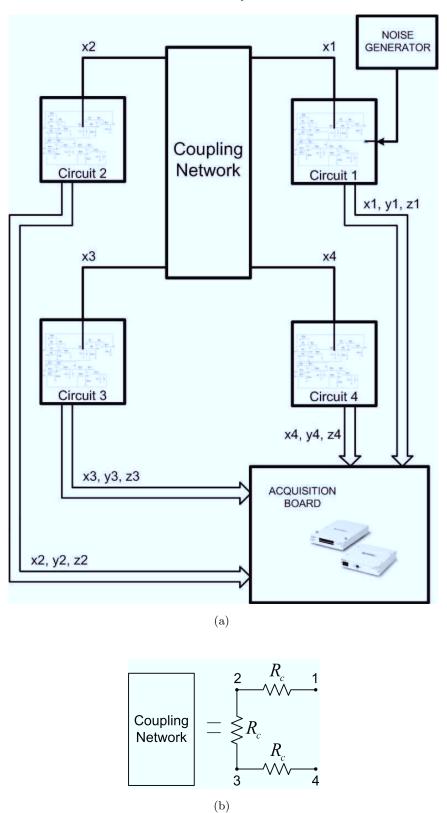

|    | 6.2   | Robustness to noise in synchronization of netwo | rk motifs | 96   |

|    |       | 6.2.1 Experimental setup                        |           | 99   |

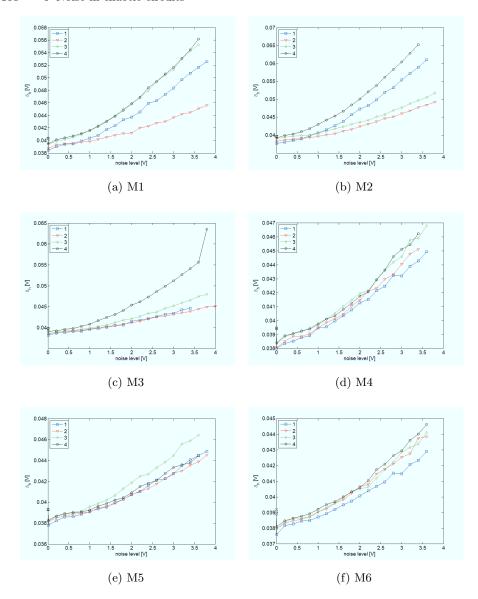

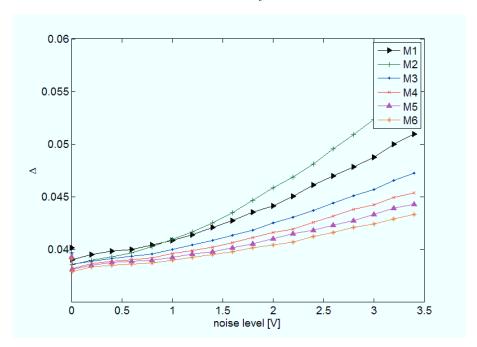

|    |       | 6.2.2 Experimental results                      |           | 104  |

| 7  | Co    | ncluding remarks                                |           | 111  |

| Re | efere | nces                                            |           | 113  |

| Pe | rson  | nal publication                                 |           | 123  |

## Introduction

This chapter briefly presents the background of the three nonlinear systems which constitute the framework in which our new nonlinear circuits have been built and new phenomena have been observed. After that, objectives of the thesis are introduced. Finally we introduce an overview of the content and the contribution of this thesis.

#### 1.1 Problem statements

There are amounts of phenomena that could be described as nonlinear systems. There, firstly we review three widely—used systems in the literature: time—delay system, Cellular Neural Network (CNN) and memristive system.

The systems with time–delays have been observed in various fields from physical systems, biological systems to engineering systems. In addition, the use of delay differential equations to model these systems has a long history. On one hand, with the presence of time–delay, the dynamics of time-delay systems are more complex than ones without delays. Using this feature, chaos can be created by using a system describing by only one delay differential equation. Applications of the time-delay chaotic systems can be found in random generator, secure communication, modelling complex system and so on. On the other hand, the presence of time-delay is able to reduce the dynamics of systems. Noticeable application is time-delay feedback control which can stabilize the chaotic behavior to one of unstable fixed points (UFPs) or unstable periodic orbits (UPOs) embedded within chaotic attractor. Time-delay feedback control has become one of the most popular methods applied successfully in a variety of biological systems, electrical circuits, lasers and magneto-elastic systems. For these reasons, design of autonomous time-delay chaotic circuits has received a significant amount of attention, the authors of many works on this subject however often built separate circumstances by changing the nonlinearities. Thus, a general design procedure is required. Moreover, although a network of T-type LCL filters was often used as the delay unit in recorded circuits, the drawbacks of parasitic resistive effects of inductances and large size make the difficulties in design progress. As the result, finding other ways to implement precise time-delay units, for example operational amplifier—based circuitries or solutions based on a digital circuitry, are open problems.

CNN is a nonlinear system which combines the advanced features of neural networks and cellular automata, hence its architecture is suitable to VLSI implementation. Applications of CNN grow continuously, for instance in fields like signal processing, pattern formation, or modelling of complex systems. There are a lot of generalizations of CNN architectures such as State Controlled–CNN, discrete–time CNN, universal machine CNN introduced just to this aim etc. . However, finding new effective architectures is still an attractive area.

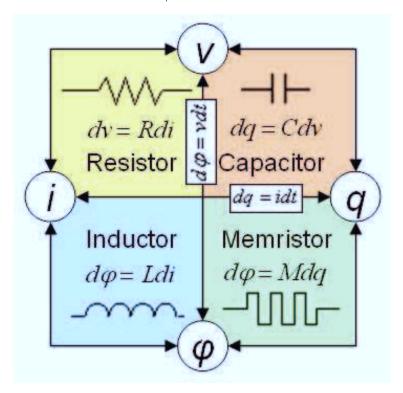

Although memristor and memristive systems have been introduced a long time ago by Chua, applications of them have developed recently after the invention of the nano-scale HP memristor. As the result, the discovery of novel memristive systems, and especially chaotic ones, is an interesting topic. While some implemented memristive circuits have exhibited chaotic behaviors, the question if it is possible to find simpler memristive chaotic circuits, i.e., 2-element circuit including a memristor and a capacitor, because of the rich of dynamics of memristor is open and very interesting.

In addition, noise can effect and modify the dynamics of original systems. Hence estimating the influence of noise on nonlinear systems, in particular novel systems or complex networks, is a very important area of research which is still ongoing.

## 1.2 Objectives

The aim of our thesis is to study nonlinear circuits built starting from devices or architectures with special features. Models of new systems are proposed and analysed. Then theoretical models are confirmed by numerical simulations and circuital experiments using off—the—shelf

#### 4 1 Introduction

analog components or Field Programmable Gate Array. Because of the rich variety of dynamics, these systems are able to be used in various applications like chaotic circuits, autowave generators or investigation of other complex phenomena. Starting from the conventional systems such as time—delay system, CNN, and memristor system, novel systems are discovered by two approaches. Changing or improving conventional systems is the method pursued in the first approach, for instance, we investigate the general methodology to design time—delay continuous—time chaotic circuit or the procedure to realize chaotic circuits with a digital time—delay block. Combining conventional systems into new ones is the main idea of the second approach, for example, the thesis focuses on studying the characteristics of memristive CNN and memristive time—delay systems. Furthermore, the presences of noise in chaotic systems are also examined.

#### 1.3 Contributions and contents

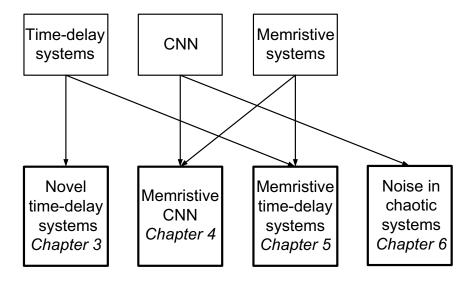

The thesis presents the obtained results relating to the novel nonlinear circuits. The structure of the thesis is illustrated in Fig. 1.1.

Chapter 2 reviews time—delay systems based on first—order delay differential equation. We summarize the nonlinearities and time-delay blocks which were employed in the literature. The design procedure for time—delay chaotic circuits is also repeated to provide a general way for construction of different time—delay circuits in the next chapter.

Fig. 1.1: Structure of the thesis which shows relations between three conventional nonlinear systems and our novel studies.

A digital approach for the implementation of time—delay blocks in chaotic circuits is discussed in Chapter 3. Because of the presence of an ADC and a DAC in the scheme, the effects of these devices are also analysed. Furthermore a general method to evaluate the effects of these parameters and/or other sources of errors or parametric differences between implementation and model are found.

CNN based on memristive cells consisting of three–component circuits is introduced in Chapter 4. Due to the fact that each cell is connected with four neighbours by four linear resistors, a diffusion–reaction

#### 6 1 Introduction

process is created. The simulations and experimental results show that our memristive CNN is able to generate autowaves.

In Chapter 5, some simple memristive time–delay systems are proposed. It is worth noting that chaos can be observed in very simple circuit configurations, for example in the 2–element circuit.

Finally, results relating to effects of noise on chaotic systems are presented in Chapter 6. There are two systems which have experimentally investigated: a chaotic system with only one stable equilibrium and a network of four Chua's circuits.

# Design of time-delay chaotic electronic circuits

This chapter summarises nonlinear blocks and delay blocks which were used to construct time—delay chaotic circuits in the literature. We also review the approach allows us to design and implement a new class of time—delay chaotic circuits with simple components, like resistors, capacitors, and operational amplifiers.

#### 2.1 Introduction

Dynamical systems with time delays are observed in various fields [118]. The presence of time delay is unavoidable because of the limit calculation speed, memory effects, finite transmission velocity etc.

On one hand, delay can be utilized to stabilize chaotic systems. Time—delay feedback control (TDFC) [83] is a highly effective control method which has applied in various systems [66, 52, 100]. The most advantage of this method is that it does not require the prior knowledge about the model. Different to the conventional feedback control,

the feedback signal is proportional to the difference of output signal and its delayed version. TDFC can stabilize the chaotic behavior to one of unstable fixed points (UFPs) or unstable periodic orbits (UPOs) embedded within chaotic attractor. There are two control parameters: the feedback gain and the feedback time delay. It is worth noticing that the feedback time—delay is often different from the intrinsic delay of time—delayed system. Two parameters have been selected by trial—and—error procedures or Lyapunov stability analysis approaches. In particular, for stabilizing of the UPO, the controller time delay has to be chosen as an integer multiple of the period of the desired UPO.

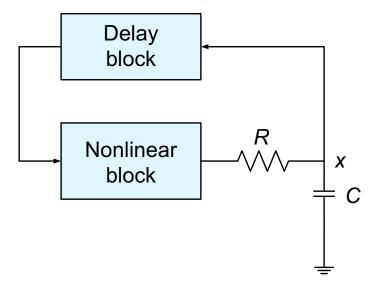

On the other hand, delay could make complex behaviors which do not exist in original systems. For example, the systems described by first order delay differential equations (DDE) can exhibit chaos [65]. These systems have attracted more attention because of their complex chaotic attractors as well as their feasibilities. Differential kinds of time-delay chaotic systems [84, 73, 125, 97, 98] have been investigated with the same structure as shown in Fig. 2.1, containing nonlinear block, delay block, and a RC filter. Observe from Fig. 2.1 that nonlinear unit has played a very important role in making diverse features of designed systems. Moreover, the normal approaches to realize delay block still faces some problems. For example, the implementation based on T-type LCL filters has the drawback of parasitic resistive effects of inductances which can not be neglected since they produce a strong attenuation of the delayed signal. The aim of this chapter is to summarize studied time-delay chaotic systems, concentrating on nonlinearity

Fig. 2.1: General architecture of the time-delay chaotic circuit.

block and time–delay block, and to review a new procedure to design time–delay chaotic circuits. That provides the background to support the next chapter where novel time–delay chaotic circuits are presented.

### 2.2 Nonlinear block

In the literature, time–delay chaotic oscillator is often presented by a DDE

$$x(t) = -ax(t) + bF(x(t-\tau)), \qquad (2.1)$$

where a, b are parameters,  $\tau$  is the time delay and F(x) is a nonlinear function. Authors focused on constructing suitable nonlinear blocks emulating F(x). Some typical nonlinear functions are reported as follows.

Mackey-Glass model [66] for haematologic disorders was given by

$$F\left(x\right) = \frac{Ax}{1+x^{10}},\tag{2.2}$$

with A = 10. This function was produced by coupling in a special way two complementary junction field–effect transistors [73].

Voss model [110] used a single-humped smooth nonlinearity

$$F(x) = A_1 x^3 + A_2 x^2 + A_3 x + A_4, (2.3)$$

with  $A_1 = -10.44$ ,  $A_2 = -13.95$ ,  $A_3 = -3.63$ , and  $A_4 = 0.85$ . The nonlinearity was built in essence from a transistor and four resistors [51].

In Ucar's works [106, 107], he developed a model containing cubic nonlinearity

$$F(x) = Ax + Bx^3, (2.4)$$

with A = 1 and B = -1. Obviously, the equation (2.4) is simpler than Eq. (2.3). Two different methods [69] were tested in order to design the cubic nonlinearity, using log-antilog operational amplifiers and analog multipliers.

Banerjee [11] defined a nonlinearity with the function

$$F(x) = 0.5A(|x| + x) + B \tanh(Cx),$$

(2.5)

where A = 1.15, B = 0.97 and C = 2.19. This function was realized easily by a half-wave rectifier and an operational amplifier.

In the neural model of Duan [38], a non–monotonously increasing transfer function was employed as activation function

$$F(x) = \sum_{i=1}^{2} A_i \left[ \tanh(x + B_i) - \tanh(x - B_i) \right], \tag{2.6}$$

where  $A_1$ ,  $A_2 = 1.5$ ,  $B_1 = 1$ , and  $B_2 = 4/3$ . The active function was implemented as a linear combinations of four translated hyperbolic tangent functions obtained by dual-transistor pairs.

Lu and He [65] introduced an odd piecewise linear function as

$$F(x) = \begin{cases} 0 & x \le -\frac{4}{3} \\ Ax - 2 & -\frac{4}{3} < x \le -0.8 \\ Bx & -0.8 < x \le 0.8 \\ Ax + 2 & 0.8 < x \le \frac{4}{3} \\ 0 & x > \frac{4}{3}, \end{cases}$$

(2.7)

with A = -1.5 and B = 1. Similar to Mackey–Glass nonlinear function, it saturates to zero at large |x|.

Another three–segment nonlinear function, which were obtained from two diodes, and an operational amplifier, has been studied [103]. It was described as

$$F(x) = \begin{cases} B(x+1) + A & x < -1 \\ Ax & -1 \le x \le 1 \\ B(x-1) + A & x > 1, \end{cases}$$

(2.8)

where A = 2.15 and B = -4.3. In contrast to the previous function (2.7), it does not saturate to zero at large |x|.

In order to increase the complex dynamics behaviours of chaotic oscillators, Wang [111] considered the activation function took a reflection symmetric piecewise linear function of the form

$$F(x) = Ax + 0.5 (A - B) [(|x + m| - |x - m|) - (|x + n| - |x - n|)],$$

(2.9)

where A = 4.3, B = -5.8, m = 1.1 and n = 3.3. The nonlinear function could be built conveniently by operational amplifiers and constant voltage sources.

Interestingly, a piecewise linear function with a threshold controller [97] was applied in the following form

$$F(x) = AF^* - Bx, (2.10)$$

where

$$F^* = \begin{cases} -x^* & x < -x^* \\ x & -x^* \le x \le x^* \\ x^* & x > x^*, \end{cases}$$

(2.11)

here A=5.2, B=3.5 and  $x^*=0.7$  is the controllable threshold value. The nonlinearity was implemented by using only two diodes and few operational amplifiers.

Moreover, first-order DDE capable of creating multiscroll chaotic attractors was researched [119, 56]. Yalcin [119] proposed a nonlinearity based on a hard limited function

$$F(x) = \sum_{i=1}^{M_x} g_{(-2i+1)/2}(x) + \sum_{i=1}^{N_x} g_{(-2i+1)/2}(x), \qquad (2.12)$$

where

$$g_{\theta}(\zeta) = \begin{cases} 1 & \zeta \ge \theta, \ \theta > 0 \\ 0 & \zeta < \theta, \ \theta > 0 \\ 0 & \zeta \ge \theta, \ \theta < 0 \\ 1 & \zeta < \theta, \ \theta < 0, \end{cases}$$

(2.13)

The system exhibited n–scroll chaotic attractor for suitable values of  $M_x$  and  $N_x$ . For example, three–, four–, five–, and six–scroll attractors obtained when  $\{M_x = 1, N_x = 1\}$ ,  $\{M_x = 1, N_x = 2\}$ ,  $\{M_x = 0, N_x = 4\}$ , and  $\{M_x = 1, N_x = 4\}$ , respectively. Nonlinear block comprised voltage comparators whose total number depending on the number of scrolls.

Recently, Kilinc [56] represented a oscillator employed the nonlinearity as a function of hysteresis series

$$F(x) = \sum_{i=1}^{N} (h(x-2i) - i) + \sum_{j=0}^{M} (h(x+2j) + j), \qquad (2.14)$$

where h(x) is the basic hysteresis function

$$h(x) = \begin{cases} -1 & x < 0.5\\ 1 & x > -0.5. \end{cases}$$

(2.15)

Similar to the previous system (2.12), by choosing the appropriate values of M and N, N+M+2 scrolls could be generated. For instance, the three–, four–, and five–scroll attractors could be observed when  $\{N=0, M=1\}$ ,  $\{N=0, M=2\}$ , and  $\{N=0, M=3\}$ , respectively. Here hysteresis comparators were realized employing positive feedback around the classical operational amplifiers.

## 2.3 Time-delay block

In the reported low–frequency time–delay chaotic circuits, the typical values of the delay were relatively large (in the order of magnitude of milliseconds). Therefore, time—delay blocks were implemented by delay lines or analog circuits.

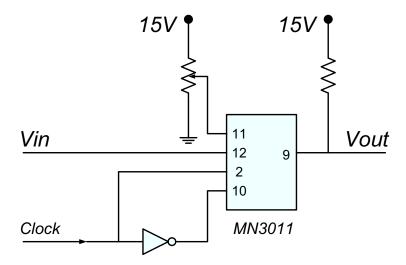

A bucket brigade delay–line device (MN3011 integrated circuit with 3328 stages) were employed [110, 51, 60] as illustrated in Fig. 2.2. The delay time may be varied by changing the clock frequency which is provided by a function generator or a special integrated circuit MN3101 that is ideally suited for driving MN3011. In fact, due to the fact that the voltages of the chaotic circuits are not within the input range of MN3011, it required additional subparts to adapt voltages. Furthermore, as the delay–line has a high frequency switch operation, a low–pass filter is required to remove the high frequency noise from the delayed voltage.

Fig. 2.2: General architecture of the delay bock based on a bucket brigade delay—line device MN3011.

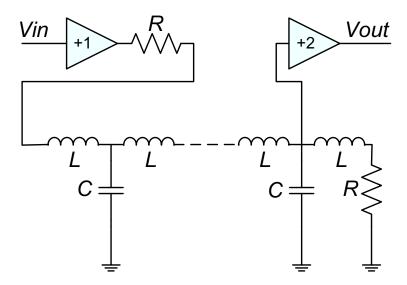

A delay block consisting of T-type LCL filters (see Fig. 2.3) was often used. This approach was introduced firstly by Namajunas [73] with matching resister at the input and output. The delay can be change by increasing or decreasing the number of LCL filters. The total delay can be calculated approximately as

$$T_{delay} = n\sqrt{2LC},\tag{2.16}$$

if n filters are utilized. Because the delay unit is frequency dependent, the cutoff frequency is only 3kHz.

Fig. 2.3: Delay block based on T-type LCL filter with  $R=190\Omega$ , L=9.5mH and C=525nF [73].

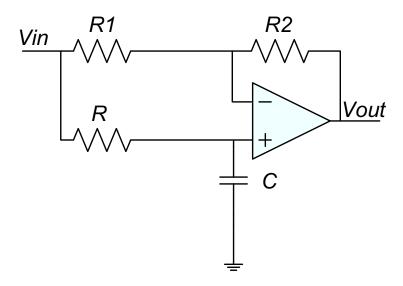

The tuning delay block can be implemented by first order all pass filter [11] as displayed in Fig. 2.4. The transfer function of an all pass filter has the following form

$$H(s) = -a_1 \frac{s - \omega_0}{s + \omega_0},\tag{2.17}$$

where the flat gain  $a_1 = 1$  is determined by  $R_1$ ,  $R_2$  and the frequency at which the phase shift is  $\pi/2$  is calculated as  $\omega_0 = \frac{1}{RC}$ . In this case, the output power level does not depend upon input signal frequency; however, the phase depends on the input signal frequency. Because each all pass filter contributes with a delay of value equal to RC, the total delay of the delay block is

$$T_{delay} = nRC, (2.18)$$

where n is the number of all pass filters. It is clear to see that by changing the value of resistor R, the amount of delay can vary, as the results the resolution of the delay block can be controlled easily.

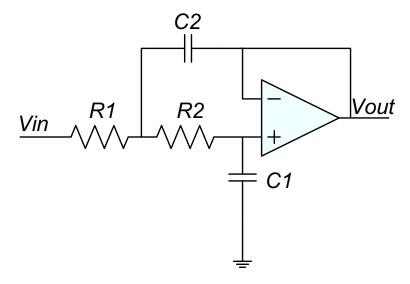

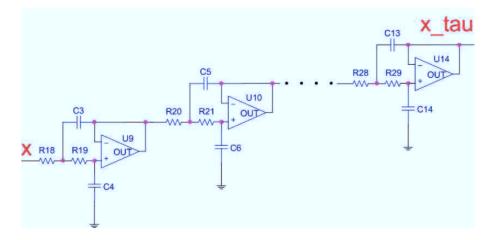

It is possible to implement the time–delay by using a cascade of n low–pass second–order Bessel filters [21]. Each filter is characterized by the Sallen–Key topology [89] as shown in Fig. 2.5 and by the following transfer function:

$$H(s) = \frac{1}{1 + C_1(R_1 + R_2)s + C_1C_2R_1R_2s^2}$$

(2.19)

The values of the filter components have been chosen in order to realize a Bessel filter with 3dB frequency equal to  $f_c \simeq 1kHz$  and taking into account off-the-shelf component values. The time-delay introduced by this filter in the band up to  $f_c$  can be calculated as  $\tau_i = -\frac{d\Phi(\omega)}{d\omega}$ . In the 3dB band,  $\tau_i \simeq C_1(R_1 + R_2)$ . For the values of the

Fig. 2.4: First-order all pass filter with  $R_1 = R_2 = 2.2k\Omega$  and C = 10nF [11].

components in Fig. 2.5  $\tau_i \simeq 0.2ms$ . Larger delays are realized by taking into account a cascade of n filters.

The approximation of an ideal delay through a cascade of multiple second—order filters or all pass filters allowed to design an efficient and simple circuitry which avoids the drawback of usual delay devices, like delay lines and LCL T—type filters. Furthermore, the filter realization with operational amplifiers, resistors and capacitors is more compact compared to LCL filters as inductors are bulky for large time—delays, although power dissipation is larger.

Fig. 2.5: Schematic of the Sallen–Key low–pass active filter implementing a low–pass Bessel filter, here  $R_1=R_2=10~\mathrm{k}\Omega,~C_1=10nF$  and  $C_2=22nF$ .

## 2.4 Design procedure for time-delay chaotic system

In this Section, we summarize the procedure to design time—delay chaotic systems using only off—the—shelf common components [21]. The core is the feedback scheme shown in Fig. 2.1 is investigated. It represents a simple feedback scheme of a nonlinear system containing all the elements strictly needed to have the possibility that chaotic behavior emerges. It consists of three blocks: a nonlinearity, a RC circuit, and a time—delay block. It represents a minimal configuration to observe chaotic dynamics in autonomous time—delay circuits. The nonlinearity is needed since chaos is a prerogative of nonlinear circuits; the RC

circuit implements the dynamics of the single state variable; and the presence of the delay makes the system infinite—dimensional, allowing chaos to be observed in a system with a single state variable.

In terms of dimensionless equations, the dynamics of the system shown in Fig. 2.1 can be expressed as follows:

$$\dot{x}(t) = k(-ax(t) - bh(x(t - \tau))) \tag{2.20}$$

where  $x(t) \in \mathbb{R}$  is the circuit state variable,  $h(x) : \mathbb{R} \to \mathbb{R}$  is the nonlinear function,  $\tau \in \mathbb{R}^+$  is the time-delay, k is a scaling factor, and a and b are system parameters. b represents the gain multiplying the nonlinearity, while ka is the pole of the RC circuit. System (2.20) represents a nonlinear system in Lur'e form with dynamical linear part given by  $L(s) = \frac{ke^{-s\tau}}{s+ka}$  and feedback nonlinear part given by  $\mathcal{N} = bh(x)$ .

For systems in Lur'e form, it is possible to analytically derive approximate conditions for the existence of chaotic behavior. They are summarized in the following criterion [45]:

Criterion 2.1 (For the Existence of Chaos in Lur'e Systems): The conditions required for the existence of chaos in a Lur'e system are:

- 1. existence of a stable predicted limit cycle;

- 2. existence of a separate unstable equilibrium point;

- 3. interaction between the unstable equilibrium point and the stable predicted limit cycle.

Additionally, it is required that the linear part has filtering properties, which in our case is always satisfied, since  $L(s) = \frac{ke^{-s\tau}}{s+ka}$ .

The existence of a stable predicted limit cycle is derived by applying the harmonic balance method [45]. A limit cycle solution of the type  $y_0(t) = A\sin(\omega t) + B$  exists if the amplitude A and the bias B of  $y_0$  satisfy the following equations:

$$1 + L(0)N_0(A, B) = 0$$

$$1 + L(j\omega)N_1(A, B) = 0$$

(2.21)

where  $N_0$  and  $N_1$  are static and dynamic describing functions [9] approximations of the nonlinearity  $\mathcal{N}$ . Solving Eqs. (2.21) means to express A as a function of B, i.e., A(B) from the static equation, and, then, to consider the intersections between the curve  $L(j\omega)$  and the curve  $-1/N_1(A(B), B)$  in the complex plane. Each intersection corresponds to a limit cycle with a given frequency and amplitude.

The stability properties of the predicted limit cycle  $y_0$  are inferred by applying the limit cycle criterion [93]:

Criterion 2.2 (Limit cycle criterion) Each intersection point of the curve  $L(j\omega)$  and the curve  $-1/N_1(A(B), B)$  corresponds to a limit cycle. If the points near the intersection, corresponding to the considered limit cycle, along the curve  $-1/N_1(A(B), B)$  for increasing values of B are not encircled by the curve  $L(j\omega)$ , then the limit cycle is stable. Otherwise the limit cycle is unstable.

Let focus on the second condition of criterion 2.1. The equilibrium points  $x(t) = x(t - \tau) = cost = \bar{x}$  of the system can be calculated by solving:

$$a\bar{x} + bh(\bar{x}) = 0 \tag{2.22}$$

The criterion for the existence of chaos in Lur'e systems requires the existence of an equilibrium point which has to be separate from the limit cycle and unstable. We now briefly discuss how the stability properties of the equilibrium points can be checked. Since in the following piece—wise linear (PWL) nonlinearities will be used, the stability of the generic equilibrium point  $E_i$  can be analyzed taking into account the following system:

$$\dot{x}(t) = k(-ax(t) - b'x(t - \tau) + u) \tag{2.23}$$

which represents the dynamics of the system (2.20) in the PWL region to which the equilibrium point under examination belongs, i.e.,  $b' = bm_i$  where  $m_i$  is the slope of the PWL nonlinearity in the region of the equilibrium point  $E_i$ . u is a generic constant input. Alternatively, if h(x) is not a PWL function, linearization around  $E_i$  could be considered.

For system (2.23) two different types of asymptotic stability can be defined [74]: delay-independent (if the system (2.23) is stable for all the values of  $\tau \in \mathbb{R}^+$ ) and delay-dependent (if the system (2.23) is stable for some values of  $\tau$  and unstable for other values of  $\tau$ ) stability. To check them, the following criteria [74] can be applied.

Criterion 2.3 (Delay-independent stability): The equilibrium point  $E_i$  is delay-independent stable if and only if a + b > 0 and  $a \ge |b|$ .

Criterion 2.4 (Delay-dependent stability): The equilibrium point  $E_i$  is delay-dependent stable if and only if b > |a|. The equilibrium point  $E_i$  is stable for  $\tau \le \tau^* = \frac{\cos^{-1}(-a/b)}{k\sqrt{(b^2-a^2)}}$ .

22

Finally, the third condition of criterion 2.1, i.e., the interaction between the stable predicted limit cycle and the unstable equilibrium point E, can be expressed as follows:

$$A \ge |E - B| \tag{2.24}$$

The system represented in Fig. 2.1 thus exhibits chaotic behavior if conditions 1)-3) of criterion 2.1 are satisfied, i.e., if Eqs. (2.21) and (2.24) admit a solution and a separate equilibrium point satisfying neither criterion 2.3 nor criterion 2.4 exists. These conditions can be satisfied by a proper choice of the nonlinearity h(x) and of the parameters a, b and  $\tau$  of system (2.20).

The time-delay  $\tau$  plays an important role in conditions 1)-3) of the criterion 2.1.  $\tau$  may change the stability properties of equilibrium points (if they are delay-dependent stable) and may also affect the Nyquist diagram of L(s) (and thus the conditions on the existence of the limit cycle and on its interaction with the equilibrium point). In general, when criterion 2.1 admits a solution, for a given nonlinearity and for fixed values of a and b, one obtains a range of values of  $\tau$ , i.e.,  $\tau_{min} \leq \tau \leq \tau_{max}$  for which the system exhibits a chaotic behavior. Once fixed  $\tau$  in this range, i.e.,  $\tau = \bar{\tau}$ , the problem of the implementation of a circuitry introducing this delay arises. Taking into account the typical scaling factor k in discrete-components circuit implementations, this delay is in the order of magnitude of milliseconds and thus its implementation requires the definition of an appropriate strategy.

The idea underlying the approach is to implement the time–delay block with a cascade of n Bessel filters which are low-pass filters with a maximally flat magnitude and a maximally linear phase response [35]. Since a Bessel filter with transfer function H(s) introduces a time–delay up to the 3dB frequency equal to  $\tau_i = -\frac{d\Phi(\omega)}{d\omega}$ , a given delay  $\bar{\tau}$  can be obtained with n blocks in cascade according to:

$$\bar{\tau} \simeq n\tau_i$$

(2.25)

In this way, the time–delay can be easily tuned by changing the number n of filters in cascade.

The Bessel filter implemented is an uncertain Bessel filter, since its implementation is based on off-the-shelf components with standard values, which additionally are subjected to tolerance. For this reason, it is important to evaluate the error between the model and the circuit implemented with a given n, and, if necessary, use a different number of filters in cascade. Since the implemented system is chaotic and thus sensitive to parameters, the introduced approach relies on the definition of an error measure taking into account this property.

Let consider two chaotic circuits coupled through a master–slave configuration [55]. If the two circuits are identical, in general, it is possible to synchronize them, obtaining state variables which asymptotically follow the same trajectory. In the case of non–identical circuits, complete synchronization cannot be obtained, but the synchronization error is kept small if the circuits have similar parameters. Therefore, the synchronization error can be used to evaluate the accuracy of the approximation based on Bessel filters.

More in detail, let consider

$$\dot{x}(t) = k(-ax(t) - bh(x(t - \tau)))$$

$$\dot{x}_n(t) = k(-ax_n(t) - bh(\hat{x}(t)) + \kappa(x(t) - x_n(t)))$$

(2.26)

where x(t) is the state variable of the ideal model (2.20), i.e., with  $L(s) = \frac{ke^{-s\tau}}{s+ka}$ ,  $x_n(t)$  is the corresponding state variable of the approximated model, i.e., with  $\widetilde{L}(s) = \frac{k}{s+ka}H^n(s)$ ,  $\kappa$  is the coupling strength, and  $\widehat{x}(t)$  is the output of the n Bessel filters in cascade, which ideally is  $\widehat{x}(t) = x_n(t-\tau)$ .

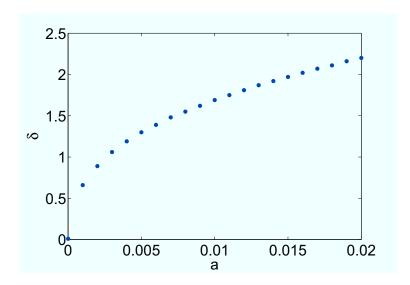

Then let define the synchronization error between the ideal model (with time–delay  $\tau$ ) and the approximated model (with a time–delay given by n filters in cascade) as follows

$$\delta(n) = \langle |x(t) - x_n(t)| \rangle \tag{2.27}$$

where  $\langle \cdot \rangle$  represents the average with respect to time. The synchronization error (2.27) is used to evaluate the accuracy of the approximated model. Moreover, n is selected to minimize this error.

The accuracy of this procedure was confirmed by experimental examples [21].

# Implementation of chaotic circuits with a digital time-delay block

In this chapter, we investigate how to implement the time—delay block with a solution based on a digital circuitry. Using available Field Programmable Gate Arrays, a programmable time—delay block can be realized. Effect of this approach to the accuracy of the whole implementation is estimated by the synchronization error.

In some electronic circuits, delay blocks are intentionally introduced to implement specific functions. For instance, in measurement applications, the highly integrated time–multiplexing device [18], the particle detector [90], and the time analog—to–digital converter [76] make use of time–delay blocks. In radio frequency applications, in high–speed microprocessors or in memories, delay circuits play an important role in delay–locked loop [24] where they allows to enhance the performance of the integrated circuits.

As noted in the previous chapter, the presence of time–delays in nonlinear systems may also induce chaotic oscillations. In such systems, the typical values of the delay may also be relatively large. In order to create time—delay, two main methodologies can be taken into account: analog methods and digital methods. In the former class, the time—delay is implemented by an analog circuit (usually a long chain of elementary blocks) made of resistors, capacitors, inductors, and/or operational amplifiers [73, 110, 85]. However, one of the disadvantages of these approaches is that they require a large number of components. Furthermore, the design or the parameters of the circuit have to be changed if other values of the delay should be implemented.

In order to overcome the drawbacks of analog methods, a few papers have explored digital approaches for the implementation of relatively small time–delays (in the order of magnitude of nanoseconds), e.g., [18, 90, 124].

The aim of this chapter is to investigate the use of time—delay digital blocks for the implementation of chaotic circuits. The effects of some parameters such as the sampling time and the number of bits used in the converters are also investigated.

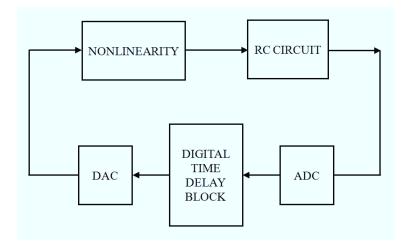

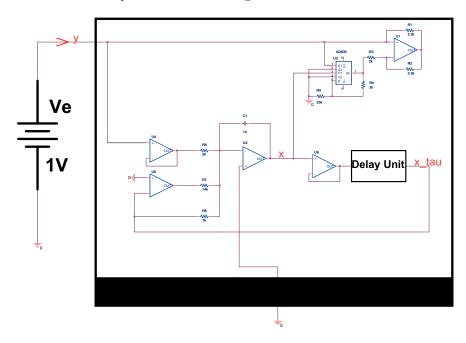

## 3.1 Design of chaotic circuits with digital time—delay block

As mentioned in Chapter 2 the model of chaotic oscillator is a simple one with only three blocks connected into a feedback configuration (see Fig. 2.1). From the point of view of the physical realization, the timedelay block implementation is not trivial, because of the typical values of the timedelay used in such chaotic oscillators (order of magnitude

of milliseconds). A digital approach is here applied for the realization of this block, the alternative scheme can be represented as in Fig. 3.1 where an analog—to—digital converter (ADC) and a digital—to—analog converter (DAC) interfacing the time—delay digital block with the remaining (analog) part of the circuit are included. The analog signal is transformed into a digital one by the ADC, then the digital signal from the ADC is delayed in the time—delay block before being fed through the DAC to the remaining part of the circuit. A delayed analog signal is obtained at the output of the DAC. The signal is delayed by a quantity given by:

$$T_{delay} = T_{ADC} + T_d + T_{DAC} \tag{3.1}$$

where  $T_{ADC}$ ,  $T_d$  and  $T_{DAC}$  are the delay of the ADC, the delay of the digital time-delay block and that of the DAC, respectively. The total delay can be approximated as  $T_{delay} \simeq T_d$  when  $T_{ADC}$ ,  $T_{DAC} \ll T_d$ .

The analog to digital conversion introduces some error sources whose effects are also investigated in this chapter. In particular, the effects of the sampling rate and of the number of bits used in the conversion process have been studied, in order to obtain indications on how to select the DAC and ADC devices in the implementation stage.

In general, the synchronization error grows up in the presence of parametric or structural differences, so the synchronization error between the circuit with a digital time—delay and the circuit with an analog time—delay can be used to evaluate the effects of the parameters of the conversion process.

Fig. 3.1: Block scheme of the time-delay chaotic oscillator with a digital time-delay block.

In the case under investigation, larger time–delays are needed, shift register–based approach has been here introduced and applied later to the circuit implementation. Since the output of a D flip–flop holds the value of the input until the next change of the clock, this device can be considered a block with a time–delay equal to the clock duration  $T_{clk}$ . A shift register made of N D flip–flops has been used in our approach. On each rising edge of the clock, a new bit is shifted in from the input and all the subsequent contents are shifted forward. The last bit in the shift register is available at the output. According to the configuration of the shift register, there are two parameters controlling the time–delay: the clock duration  $T_{clk}$  and the number of shifted bits  $N_{shift}$ . The time–delay introduced by a shift register is given by:

$$T_{delay} = T_{clk} N_{shift} (3.2)$$

An advantage of this digital implementation, compared to analog approach for delay implementation, is the possibility to use available programmable hardware to realize the desired configuration and to change its parameters on—the—fly. In the following, we describe one of such implementations, in particular based on an FPGA, and show its suitability for the implementation of chaotic circuits.

## 3.2 FPGA-based implementation

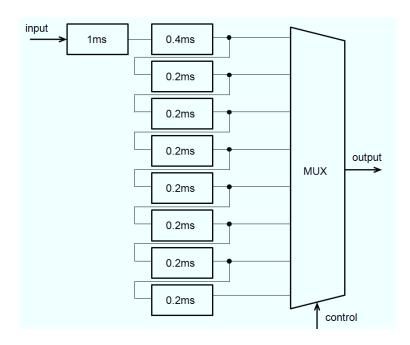

#### 3.2.1 Implementation of the time-delay

High performance FPGAs containing millions of gates are currently available in the market [70]. FPGAs can be used in almost all applications including communications, digital signal processing applications or systems on chip, because of their advanced features such as embedded microprocessor and digital signal processing cores. An FPGA can be quickly configured to the desired application so that it is very convenient for the research and prototype development phase. For these reasons, in this chapter for the implementation of the time–delay block, an FPGA has been chosen. In this Section, the details of the implementation of the time–delay block are outlined.

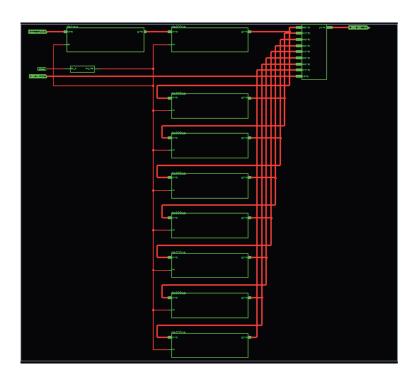

The scheme of the time–delay block implemented in the FPGA is illustrated in Fig. 3.2. It consists of one multiplexer and nine time–delay subcircuits connected in cascade (including one subblock implementing a delay of 1 ms, one subblock implementing a delay of 0.4 ms and seven identical subblocks implementing a delay of 0.2 ms). The time–delay

subcircuits utilize shift register configurations as described in Sect. 3.1. The subcircuits are connected to the multiplexer so that a total delay in the range from 1.4 ms to 2.8 ms can be set. The tuning of the timedelay has been made accessible to the user, by implementing a routine, which thanks to control buttons, allows the user to set the multiplexer parameters, thus selecting the desired time-delay.

Fig. 3.2: Block diagram of the time–delay block implemented in the FPGA.

The hardware platform used in this work is the ML405 board that is based on the Virtex4 family of FPGAs. The main features of the board are the following: Virtex-4 FPGA XC4VFX20-FF672, 128 MB DDR SDRAM with a 32-bit interface running up to 400 MHz data rate, 100

MHz clock oscillator plus one extra open 3.3 V clock oscillator socket. The delay circuitry prototype has been realized in the Xilinx FPGA chip programmed through a VHDL language. By employing the RTL Viewer tool in Xilinx ISE, the schematic diagram of the delay block could be obtained as in Fig. 3.3. The main resources of Virtex4 used for our application are summarized in Table 3.1.

Fig. 3.3: Schematic of the time–delay block displayed by RTL Viewer tool.

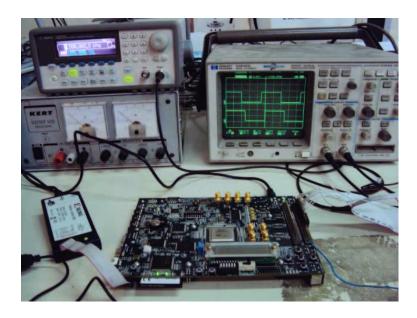

It is interesting to note that the time—delay block could be tested by applying directly a digital signal input generated by the signal generator (see Fig. 3.4). Both the input and output signal were displayed on

Table 3.1: Device utilization summary

| Logic utilization          | $\mathbf{Used}$ | $\mathbf{A}$ vailable | Utilization |

|----------------------------|-----------------|-----------------------|-------------|

| Number of Slice Flip Flops | 442             | 17,088                | 2.62%       |

| Number of 4 input LUTs     | 73              | 17,088                | 0.43%       |

the monitor of the oscilloscope, so it was convenient to see and compare results.

Fig. 3.4: Connection of equipments to test the FPGA–based time–delay block.

#### 3.2.2 Implementation of the chaotic circuit

In this Section, an example of a chaotic circuit obeying (2.1) is discussed. The chaotic circuit is described by the following state equation [52]:

$$\dot{x} = -ax(t) - b\sin(x(t-\tau)), \qquad (3.3)$$

where a and b are the parameters and  $\tau$  is the dimensionless timedelay. Equation (3.3) represents the dynamics of an optical bistable resonator in which x is the lag of the phase of the electric field across the resonator, b is the laser power intensity injected into the system, and  $\tau$  is the round trip time of the light in the resonator.

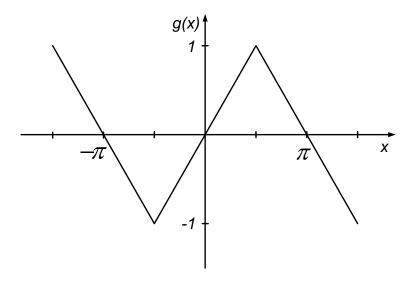

In the following, instead of implementing the sinusoidal nonlinearity appearing in (3.3), a piecewise linear (PWL) approximation has been used. PWL functions, in fact, have the advantage of ease of implementation [43].

In particular, the following PWL approximation has been used:

$$\sin x \simeq g(x) = \begin{cases} -\frac{2}{\pi}x - 2, & x \in \left[ -\frac{3\pi}{2}; -\frac{\pi}{2} \right] \\ \frac{2}{\pi}x, & x \in \left[ -\frac{\pi}{2}; \frac{\pi}{2} \right] \\ -\frac{2}{\pi}x + 2, & x \in \left[ \frac{\pi}{2}; \frac{3\pi}{2} \right] \end{cases}$$

(3.4)

The nonlinear in (3.4) is also presented in Fig. 3.5

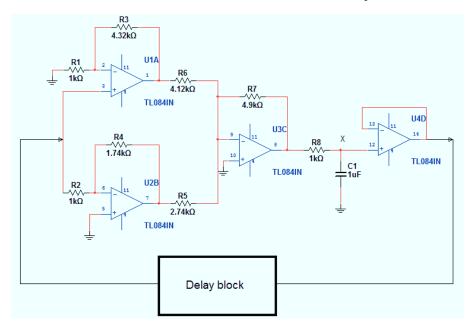

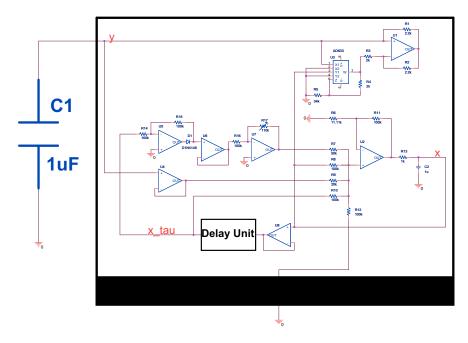

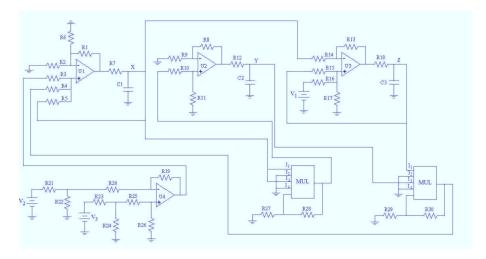

The complete schematics of the designed time-delay chaotic circuit including the PWL function (3.4), the time-delay block implemented with the FPGA approach described in Sect. 3.2.1 and the RC circuit, is shown in Fig. 3.6. The circuit makes use of TL084 operational amplifiers (U1A, U2B, U3C, and U4D), eight resistors (from R1 to R8) with 5%

Fig. 3.5: Piece—wise linear function g(x).

tolerance, one capacitor (C1), and the FPGA-based time-delay block.

The first three operational amplifiers are used to build the PWL nonlinearity by letting the operational amplifiers U1A and U2B working in the nonlinear region according to the guidelines described in [43]. The operational amplifier U4D is a buffer. The time–delay block is obtained through the FPGA which implements a time–delay  $\tau$  given by:

$$\tau = \frac{T_{delay}}{R_8 C_1},$$

where  $T_{delay}$  is tuned through control buttons that set the FPGA multiplexer configuration.

By applying the Kirchhoff's laws and taking into account the parameter values reported in Fig. 3.6, the following differential equation

Fig. 3.6: Electrical scheme of the time–delay chaotic circuit introduced in this chapter. The delay block is implemented by means of a FPGA.

describing the circuit dynamics can be obtained:

$$\frac{dV_{C_1}}{dt} = -aV_{C_1}(t) - bg\left(V_{C_1}(t - \tau)\right)$$

where a = 1, b = 5 and  $V_{C_1}$  is the voltage across the capacitor  $C_1$ .

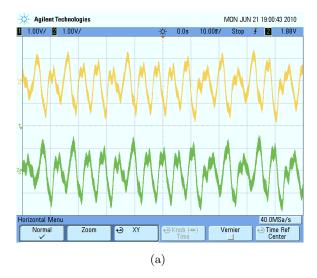

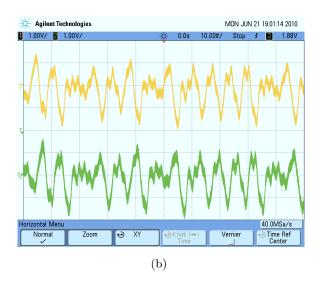

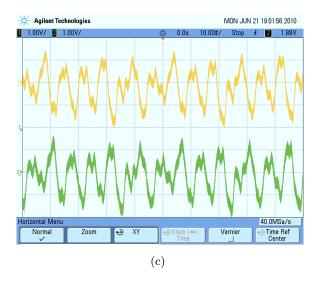

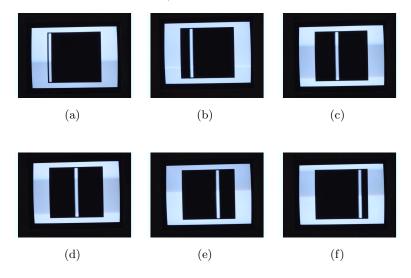

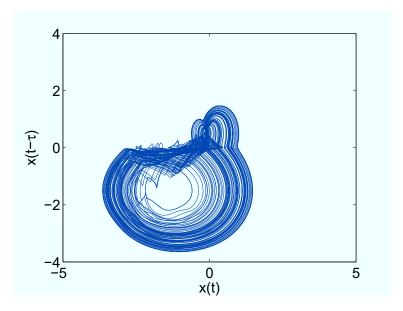

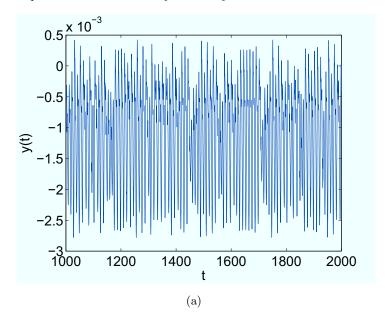

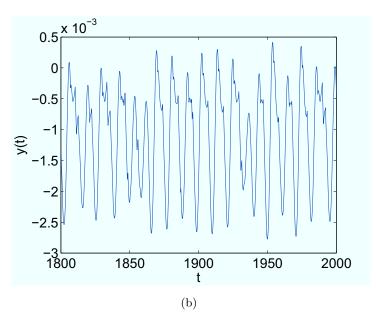

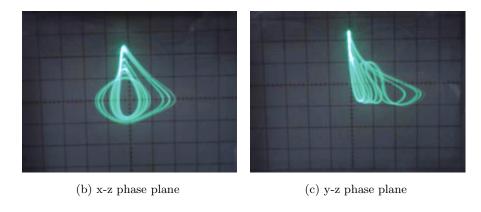

In the range of t from 1.6 ms to 2.8 ms, the circuit displays a chaotic regime, as theoretically expected [22]. Figure 3.7 shows some examples of the waveforms experimentally obtained. These experimental results confirm that the FPGA-based delay block performs effectively for generating chaos.

Fig. 3.7: Waveforms generated by the chaotic circuit of Fig. 3.6 for different values of the time–delay: (a)  $\tau$  =2.0 ms; (b)  $\tau$  =2.4 ms; (c)  $\tau$  =2.8 ms.

### 3.3 Accuracy of the implementation

As mentioned in Sect. 3.1, the conversion process affects the accuracy of the implementation. The accuracy of the implementation has been investigated by assuming as a reference model an analog implementation based on Bessel filters and described in [22] and investigating how the synchronization error between the analog implementation and the FPGA-based one is affected by the parameters of the conversion processes (the sampling rate and the number of the bits used).

In particular, an unidirectional coupling scheme [19] has been implemented. The first chaotic system, referred as the master, sends a scalar signal (i.e., the state variable x) to the second system, referred as the slave. At the slave, the state variables of the two systems are compared and used to build the error signal  $e(t) = x_m(t) - x_s(t)$  which is then fed back to the slave, like in an observer. More in detail, the master equation and the slave equation can be written as:

$$\dot{x}_{m}(t) = -a_{m}x_{m}(t) - b_{m}\sin(x_{m}(t-\tau))

\dot{x}_{s}(t) = -a_{s}x_{s}(t) - b_{s}\sin(x_{s}(t-\tau)) + K(x_{m} - x_{s}).$$

(3.5)

The synchronization error has been defined as follows:

$$E = \frac{1}{N} \sum_{i=1}^{N} e(t_i)$$

(3.6)

where  $t_1, t_2, \ldots, t_N$  are the sampling times for each time series and N is the total number of samples.

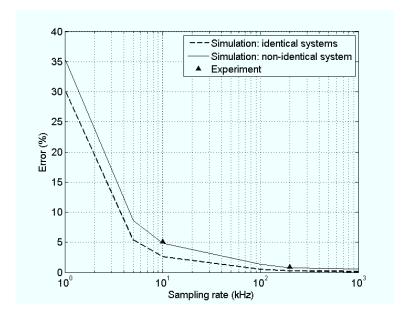

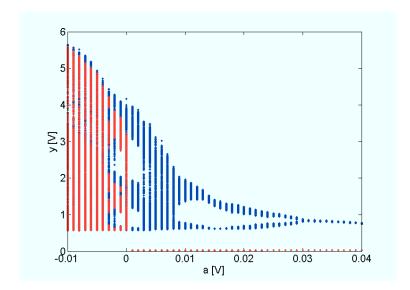

To evaluate how these parameters affect the synchronization error, both numerical simulations with respect to different parameters of the conversion process and experiments in different conditions have been performed. As numerical simulations are concerned, two different cases have been taken into account: identical and nonidentical systems. In the case of identical systems, the parameters appearing in (3.3) have been fixed equal for the two circuits  $a_m = a_s = a = 1$  and  $b_m = b_s = b = 5$ . In contrast, the case of nonidentical systems, the parameters have been supposed to be affected by a tolerance in the order of magnitude of 5% of the nominal value, i.e.,  $a_m = a$ ,  $a_s = a(1 \pm 0.05)$ ,  $b_m = b$ , and  $b_s = b(1 \pm 0.05)$ . As it will be shown later, the introduction of the tolerance in the numerical simulations is needed to obtain a good match with the experimental simulations. In fact, the introduced tolerance is in the range of parameter tolerance of the circuit components used.

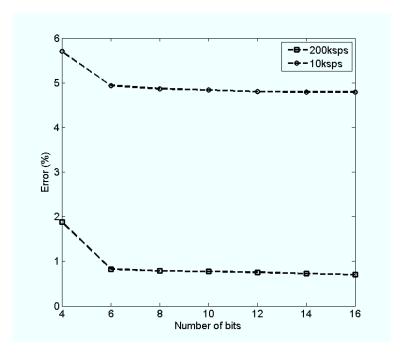

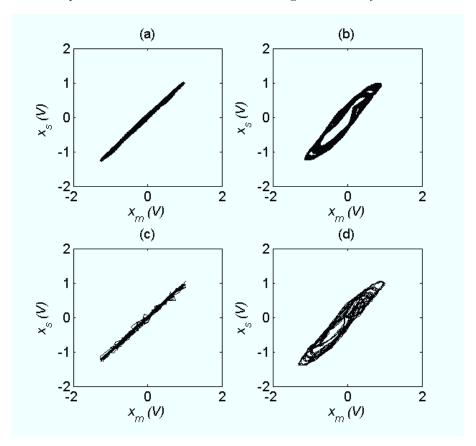

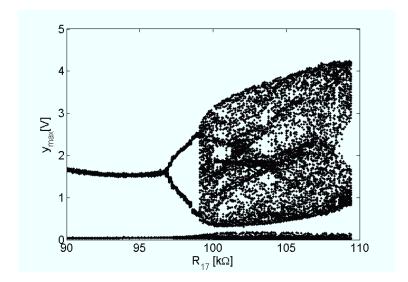

The results obtained have been reported in Fig. 3.8 and Fig. 3.9 showing the synchronization error versus the sampling rate and the number of bits, respectively. Figure 3.8 indicates that the sampling rate has to be chosen higher than 100 kHz in order to guarantee a low synchronization error. The synchronization error increases significantly when the sampling rate goes under 100 kHz. As regards the number of bits of the conversion process, when it increases, the synchronization error shows small decreases as illustrated in Fig. 3.9. Therefore, it is not convenient to increase the number of bits beyond 8–10 bits. The synchronization error corresponding to a sampling frequency  $f_s = 10$  kHz is always higher than the synchronization error obtained with a sampling frequency  $f_s = 200$  kHz, independently of the number of bits used. Based on these considerations, the ADC and DAC used have been

selected with a number of bits equal to 8 and  $f_s = 200$  kHz. The results shown in Fig. 3.7 refer to this case.

Fig. 3.8: Numerical results: synchronization error (3.6) between model with analog time–delay block and model with digital time–delay block versus sampling rate.

The data in the experiments have been acquired by using a data acquisition board (National Instruments USB-6255) with sampling frequency  $f_s = 300$  kHz. As mentioned before, the accuracy of the implementation was evaluated by assuming as reference model a totally analog implementation in which the time-delay block has been realized with Bessel filters [22]. This totally analog implementation has been assumed as the master circuit, while the slave is the FPGA-based

Fig. 3.9: Numerical results: synchronization error (3.6) between model with analog time—delay block and model with digital time—delay block versus number of bits.

time–delay chaotic circuit. Synchronization is observed, as shown in Fig. 3.10(a) when the high speed analog–to–digital converter and high speed digital–to–analog converter (maximum throughput of 200 kHz) are used in the slave circuit. In contrast, when the ADC and DAC with large conversion time (low throughput of 10 kHz) are utilized, a much larger synchronization error occurs as shown in Fig. 3.10(b). It is worth noting that the conversion process parameters, especially the sampling rate, critically affect dynamical features of the circuits which were represented through the synchronization error. The synchronization errors

in Fig. 3.10(a) and Fig. 3.10(b) are equal to E = 0.8948% and E = 5.1212%, respectively (they have been evaluated taking into account an acquisition time window equal to 1 s). These experimental results well fit the simulation results, in the case of nonidentical systems, i.e., when the parameter tolerance of the circuit components used is taken into account, as it can be observed in Fig. 3.8.

The procedure described to evaluate the effects of the conversion parameters can be applied when a reference model does exist, which is obviously not the general case. Therefore, a more general strategy is here described. The idea is to acquire a long trajectory from the circuit and to use it to synchronize the slave circuit. Instead of the master signal  $x_m$ , the acquired signal is used. The experiment, previously described, was repeated by using this approach. First, a circuit with high speed analog-to-digital and digital-to-analog converters has been used. In this case, a low synchronization error (E = 0.9687%) has been observed as shown in Fig. 3.10(c). On the opposite, when a low sampling rate 10 kHz ADCs and DACs is used, the synchronization error (E = 5.2375%) grows up as shown in Fig. 3.10(d). The experimental results obtained confirmed that investigating synchronization by using a signal acquired from the chaotic circuit itself is a suitable strategy for the evaluation of the effects of the conversion parameters (or more in general of other parameters) on the accuracy of the implementation.

Fig. 3.10:  $x_s$  vs  $x_m$  for (a) analog master/FPGA-based slave with high speed ADC; (b) analog master/FPGA-based slave with low speed ADC; (c) FPGA-based master with high speed ADC/FPGA-based slave with high speed ADC, (d) FPGA-based master with low speed ADC/FPGA-based slave with low speed ADC/FPGA-based slave with low speed ADC.

# Memristive Cellular Neural/Nonlinear Networks

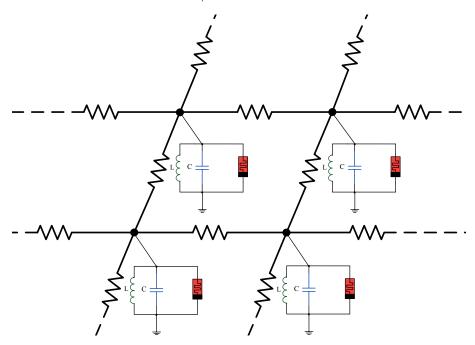

Memristor has received a significant amount of attention after a solid state implementation of it was realized in the Hewlett-Packard laboratories, because of the potential applications of such device in different areas. In this chapter, we introduce a Cellular Neural/Nonlinear Network based on memristive cells for autowave generation. The basic cell consists of a three-component circuit (the parallel of a capacitor, an inductor and an active memristor) and displays slow-fast dynamics. Such circuit is then connected through passive resistors to other identical cells to form a reaction-diffusion system. Simulation results show that the system is able to generate autowaves and open the way to the study of other complex phenomena like spiral waves or pattern formation in memristive circuits. Moreover, we also implement such a *Memristive* Cellular Neural/Nonlinear Network (MCNN) by using Field Programmable Gate Array (FPGA). Our system consisting of a FPGA development board connected to a monitor allows us

to emulate autowave propagation in an efficient way. Experimental results show the feasibility of FPGA-based approach to implement MCNN.

#### 4.1 Autowaves in Cellular Neural Network

Cellular Neural/Nonlinear Networks (CNNs) were invented to process real—time signals [33], especially image signals [32]. The classical CNN configuration includes a number of cells which consist of linear capacitors, linear resistors, linear and nonlinear voltage—controlled current sources and independent sources. Hence, VLSI implementation of the CNN was realized conveniently with CMOS technique [31]. Because CNNs have the ability to emulate partial differential equations, they can be utilized to simulate complex phenomena in the space such as autowaves [78], [6], spiral waves [77] or Turing patterns [48]. It is interesting to note that chaotic circuits could be also realized by generalized CNN cells [4], [5].

Recently, the nanoscale memristor has been found [99], [105], although the fundamental theory of it was already introduced [27] and generalized [30] some time ago. This discovery promised to apply for biological models [79], adaptive filters [37] or programmable analog integrated circuits [92, 28]. The potential applications of memristive systems lead to one question. How complex systems made by interacting memristor—based circuits can be constructed? There are a few studies focusing on this question. In [54], a cellular automaton and

a discrete-time CNN (DTCNN) using nonlinear passive memristors were designed. One noticeable feature of memristive DTCNN was the multitasking, since memristive DTCNN were shown to be able to perform more than one functions of the memristor cellular automaton at the same time. Another approach was the use of standard CNNs to implement memristive analog circuits which then can be utilized as basic cells to realize chaotic circuits [20]. In another work [61], the role of memristors in implementing programmable connections of the cells was investigated. Following these discoveries, in this chapter we introduce a novel memristive CNN, named MCNN, and we show that it can exhibit autowaves. This MCNN represents an universal paradigm following a process of generalization schematically shown in Fig. 4.1. In fact, the invention of the memristor leads to a new paradigm in which four components are at the basis of any electrical circuit, as shown in Fig. 4.1. Based on this new component, novel dynamic, eventually chaotic, circuits can be designed. In turn these can be used as basic cells to define novel CNN architectures with general features. In the following we describe one of such architectures and show that it can generate autowaves.

#### 4.1.1 Model of the memristive CNN

CNNs are usually based on first-order cells [31]. Cells are directly connected with their neighbours, but the global interaction is guaranteed because of indirect effects. CNN, in fact, includes both advanced features of neural network and cellular automata such as asynchronous

Fig. 4.1: Schematic representation of the four basic components of electrical circuits.

parallel processing, continuous—time dynamics and practical implementation. CNNs have applied in various areas: image signal processing, pattern recognition [32], bio—inspired robotic visions and biological functions [41].

When CNNs are made up of more complex cells (the cell itself can be a complex circuit, e.g., a Chua's circuit), difficult computational problems can be reformulated naturally by CNN. These CNN arrays have been examined for the generation of Turing patterns and various autowaves [29], where CNNs were used to approximate partial differential equations, especially reaction—diffusion equations. In our case, we adopt this second approach to explore complexity through memristive CNN. In this Section we represent the details of the fundamental memristive cell introduced as well as the overall configuration of our MCNN.

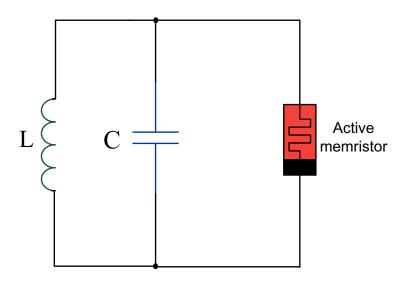

#### The memristive cell

In their work, Itoh and Chua introduced a gallery of different memristive oscillators [53]. Some of these oscillators are also able to display chaotic dynamics. Among the oscillators introduced in [53], to construct the basic cell used in our investigation, we choose a simple one, the so-called memristor-based Chua oscillator with a flux controlled memristor. The circuit of the cell is illustrated in Fig. 4.2, where it can be observed that the cell includes three elements: an inductor, a capacitor, and an active memristor. It is worth to notice that the active memristor consists of a negative conductance (-G) and a passive memristor in parallel.

The dynamic equations of the cell are derived by applying Kirchhoff's circuit laws as follows

$$\begin{cases}

C\dot{v} = -i - W(\varphi)v + Gv, \\

L\dot{i} = v, \\

\dot{\varphi} = v,

\end{cases}$$

(4.1)

where v, i, and  $\varphi$  are voltage of the capacitor, current over inductor, and flux, respectively. The memristor is characterized by the memductance

$$W(\varphi) = \frac{dq(\varphi)}{d\varphi} = \begin{cases} a & |\varphi| < 1, \\ b & |\varphi| > 1, \end{cases}$$

$$(4.2)$$

where  $q(\varphi)$  is a piecewise-linear function described by

$$q(\varphi) = b\varphi + 0.5(a - b)(|\varphi + 1| - |\varphi - 1|). \tag{4.3}$$

By replacing x = v, y = i,  $z = \varphi$ ,  $\alpha = 1/C$ ,  $\beta = 1/L$ , and  $\gamma = G$ , Eqs. (4.1) can be transformed into the following dimensionless equations:

$$\begin{cases} \dot{x} = \alpha \left( -y - W(z) x + \gamma x \right), \\ \dot{y} = \beta x, \\ \dot{z} = x, \end{cases}$$

$$(4.4)$$

From Eqs. (4.4) we can obtain

$$\dot{y} - \beta \dot{z} = 0. \tag{4.5}$$

Computing z in Eq. (4.5) yields

$$z = \frac{y+c}{\beta},\tag{4.6}$$

where c is constant. Substituting Eq. (4.6) into Eq. (4.4), the following equation describing the dynamics of the memristive cell is obtained:

$$\ddot{y} + \alpha \left( W \left( \frac{y+c}{\beta} \right) - \gamma \right) \dot{y} + \alpha \beta y = 0. \tag{4.7}$$

The memristive circuit can be thus considered as a periodic second—order oscillator. Eq. (4.7) is equivalent to Eqs. (4.4). In the following, our analysis is however referred to Eqs. (4.4).

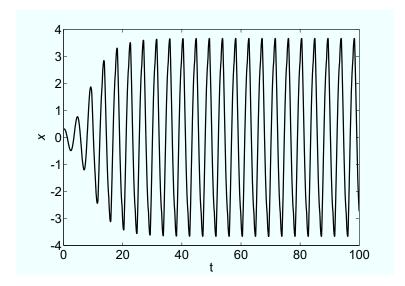

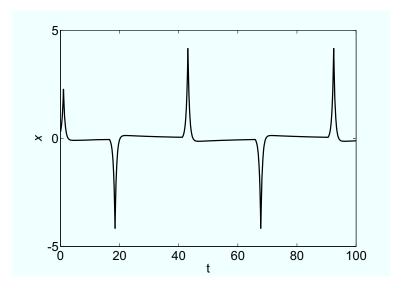

When the parameters are chosen such as  $\alpha=2,\,\gamma=0.3$ ,  $\beta=1,\,a=0.1,$  and b=0.5, Eqs. (4.4) exhibit the periodical signal shown

in Fig. 4.3. However, in order to get autowaves, Eqs. (4.4) should be characterized by a slow–fast dynamics [77], [7]. In the slow regime, the state of the limit cycle remains at a constant value for a considerably long period of time  $\tau_{st}$ . After this long period, the state returns rapidly in a significantly short period of time  $\tau_{ex}$ , where  $\tau_{ex} << \tau_{st}$ . By choosing appropriate parameters e.g.,  $\alpha = 10$ ,  $\gamma = 0.3$ ,  $\beta = 0.01$ , a = 0.1, and b = 0.5, our memristive cell satisfies this requirement. The waveform of the signal (variable x(t)) is shown in Fig. 4.4, in which the slow–fast dynamics is clearly evident.

Fig. 4.2: The memristive cell.

#### Memristive CNN

In the literature, the autowaves were implemented by 1D CNNs, 2D CNNs or CNNs made of Chua's circuits. In [81] travelling waves, a

Fig. 4.3: Waveform of signal x when the parameters are chosen as  $\alpha=2,\,\gamma=0.3$  ,  $\beta=1,\,a=0.1,$  and b=0.5.

special case of autowaves, were studied in the 1D and 2D CNNs where the cell has two stable equilibrium points. The travelling waves only triggered from one stable equilibrium state to a second one and they remained from then on. Arena et al. [7] utilized the two–layer CNN model with second–order cells to obtain various complex phenomena such as autowaves, and Turing pattern formation, thus demonstrating that state–controlled CNNs give a physical realization of low–cost soft–computing devices.

We construct a MCNN as shown in Fig. 4.5. Each cell is connected with four neighbours by four linear resistors. As the result, a reaction—diffusion process is emulated.

From Fig. 4.5 the dynamic equations of the MCNN are derived

Fig. 4.4: Waveform of signal x when the parameters are chosen as  $\alpha = 10, \gamma = 0.3$ ,  $\beta = 0.01, a = 0.1$ , and b = 0.5.

$$\begin{cases} \dot{x}_{i,j} = \alpha \left( -y_{i,j} - W \left( z_{i,j} \right) x_{i,j} + \gamma x_{i,j} \right) \\ + D \left( x_{i-1,j} + x_{i+1,j} + x_{i,j-1} + x_{i,j+1} - 4x_{i,j} \right), \\ \dot{y}_{i,j} = \beta x_{i,j}, \\ \dot{z}_{i,j} = x_{i,j}, \end{cases}$$

$$(4.8)$$

where the diffusion coefficient D is constant.

#### 4.1.2 Simulation results

The term *autowaves* or *autonomous waves* was introduced by R. V. Khorhlov [49]. Typical examples of autowaves include the waves of combustion, of phase transitions, concentration waves in chemical reactions, and also many biological autowave processes. According to [78], the autowaves have some noticeable properties as follows. The ampli-

Fig. 4.5: Block diagram of the proposed memristive CNN.

tude and shape of the autowave do not change during propagation. Autowaves do not exhibit reflection or interference, but annihilation occurs when two waves collides. In this Section, the simulation results are reported to illustrate the principal features of autowaves in the MCNN.

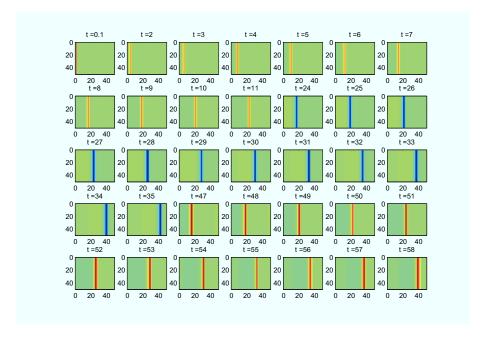

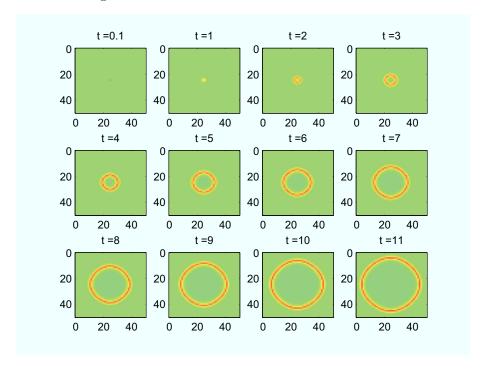

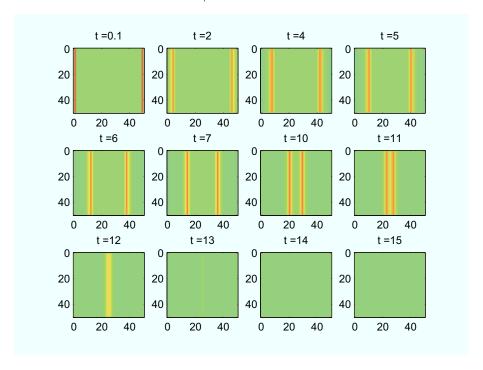

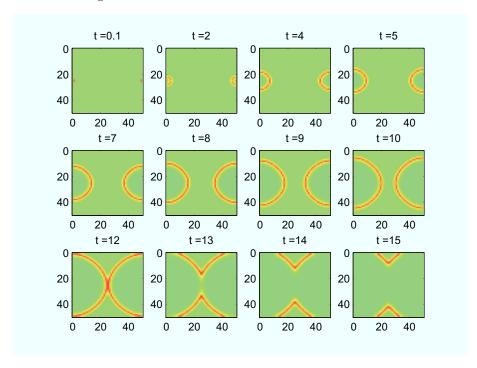

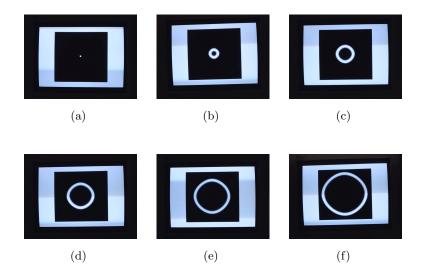

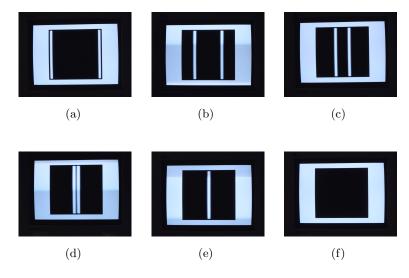

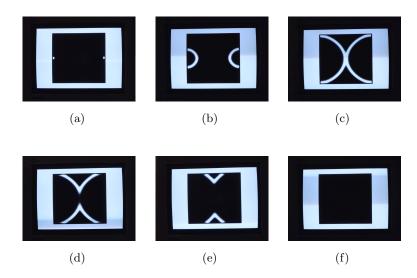

A 50 × 50 MCNN with zero–flux boundary conditions has been simulated. Here, the diffusion coefficient was fixed to D=0.51. We used the following initial conditions:  $x_{i,j}(0)=y_{i,j}(0)=z_{i,j}(0)=0$ , where  $1 \le i, j \le 50$ , except  $x_{i,2}(0)=1.5$  in Fig. 4.6,  $x_{25,25}(0)=1.5$  in Fig. 4.7,  $x_{i,2}(0)=x_{i,49}(0)=1.5$  in Fig. 4.8 and  $x_{25,2}(0)=x_{25,49}(0)=x_{26,2}(0)=x_{26,49}(0)=1.5$  in Fig. 4.9.

An autowave has been observed moving with the same shape, from the left-hand side to the righ-hand side of the MCNN, as shown in Fig. 4.6. Unlike classical waves whose amplitude attenuates rapidly with the distance, the shape of autowave remains unchanged. When one point at the centre of the MCNN is active, an autowave propagates and a circle-shape appears as given in Fig. 4.7.

Fig. 4.8 represents two autowaves propagating from the left—hand side and the right—hand side as an effect of the initial conditions considered. The two waves move with the same velocity, finally annihilate each other when the two wavefronts collide with each other. Similarly, two colliding autowaves annihilate rather than penetrating one another, and, therefore, no interference takes place as shown in Fig. 4.9. The major characteristics of autowaves were therefore observed in the MCNN, thus showing the effectiveness of the introduced structure to generate autowaves. It is worth to notice that autowaves are generated with a very simple basic cell consisting of three components and, in view of the considerations in [72], in principle, even a simpler cell (consisting of either a capacitor or an inductor and an active memristor) can be used.

## 4.2 FPGA-based generation of autowaves in Memristive Cellular Neural Networks

Different hardware implementations of CNN systems emulating autowave propagation have been also proposed: for instance, Gomez-

Fig. 4.6: 2D representation of an autowave propagating from the left–hand side to the right–hand side of a MCNN.

Gesteira et al. [47] designed a two–dimensional array (10 × 8 circuits) where every cell is a Chua's circuit; Yalcin and Suykens [120] demonstrated spatio–temporal pattern formation on the ACE16k CNN chip; and Yeniceri and Yalcin [123] proposed a real–time implementation of autowave generation on FPGA.

In this Section we consider CNNs made of memristor—based cells and implemented through FPGA and show that they can generate autowaves. While single memristor—based nonlinear circuits were focused in [53, 72, 71], as far as complex systems made of more interacting units are concerned we mention here a few examples. In [54], a cellular automaton and a discrete—time CNN (DTCNN) using nonlinear pas-

Fig. 4.7: Formation of an autowave from the centre of the MCNN.

DTCNN was the multitasking, since memristive DTCNN were shown to be able to perform more than one functions of the memristor cellular automaton at the same time. Another approach was the use of standard CNNs to implement memristive analogue circuits which then can be utilized as basic cells to realize chaotic circuits [20]. In another work [61], the role of memristors in implementing programmable connections of the cells was investigated. In Sect. 4.1 it has been shown that CNNs with memristive cells can generate autowaves. We investigate here an FPGA-based approach for the implementation of this model. The choice of the FPGA as a platform for the hardware imple-

Fig. 4.8: Obliteration of two colliding autowaves, travelling from the left–hand side and the right–hand side.

mentation of the system is motivated by the fact that FPGA combines the advantages of both hardware and software systems by providing reprogrammable hardware.

## 4.2.1 FPGA-based implementation of Memristive Cellular Neural Networks

FPGA-based implementations concentrating on circuit architectures have been widely used for signal processing [86]. New algorithms can be easily tested with the FPGA development platform that reduces time consumption as well as the price of the process of design [57].

Fig. 4.9: Annihilation of two colliding autowaves.

In order to realize a system based on FPGA, its discrete model is required firstly. There, a discrete-time version of Eqs. (4.8) is obtained by applying the fourth–order Runge–Kutta integration method [82] as follows:

$$\begin{cases} x_{i,j} (k+1) = x_{i,j} (k) \\ + \frac{h}{6} (k_{1x;i,j} + 2k_{2x;i,j} + 2k_{3x;i,j} + k_{4x;i,j}), \end{cases}$$

$$\begin{cases} y_{i,j} (k+1) = y_{i,j} (k) \\ + \frac{h}{6} (k_{1y;i,j} + 2k_{2y;i,j} + 2k_{3y;i,j} + k_{4y;i,j}), \end{cases}$$

$$z_{i,j} (k+1) = z_{i,j} (k) \\ + \frac{h}{6} (k_{1z;i,j} + 2k_{2z;i,j} + 2k_{3z;i,j} + k_{4z;i,j}), \end{cases}$$

$$k_{nx;i,i}, k_{nx;i,j} \text{ and } k_{nx;i,j} (n = 1, 2, 3, 4) \text{ are evaluated as}$$

where  $k_{nx;i,j}$ ,  $k_{ny;i,j}$  and  $k_{nz;i,j}$  (n = 1, 2, 3, 4) are evaluated as

$$\begin{cases} k_{1x;i,j} = \alpha \left( -y_{i,j} \left( k \right) + \gamma x_{i,j} \left( k \right) - W \left( z_{i,j} \left( k \right) \right) x_{i,j} \left( k \right) \right) \\ + D \left( x_{i-1,j} \left( k \right) + x_{i+1,j} \left( k \right) + x_{i,j-1} \left( k \right) \right) \\ + x_{i,j+1} \left( k \right) - 4 x_{i,j} \left( k \right) \right), \end{cases}$$

$$\begin{cases} k_{1y;i,j} = \beta x_{i,j} \left( k \right), \\ k_{1z;i,j} = x_{i,j} \left( k \right), \end{cases}$$

GA-based generation of autowaves in Memristive Cellular Neural Network

$$\begin{cases} k_{2x;i,j} = \alpha \left[ -y_{i,j} \left( k \right) - \frac{h}{2} k_{1y;i,j} + \gamma \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j} \right) \right. \\ \left. - W \left( z_{i,j} \left( k \right) + \frac{h}{2} k_{1z;i,j} \right) \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j} \right) \right] \\ \left. + D \left[ x_{i-1,j} \left( k \right) + \frac{h}{2} k_{1x;i-1,j} + x_{i+1,j} \left( k \right) \right. \\ \left. + \frac{h}{2} k_{1x;i+1,j} + x_{i,j-1} \left( k \right) + \frac{h}{2} k_{1x;i,j-1} + x_{i,j+1} \left( k \right) \right. \\ \left. + \frac{h}{2} k_{1x;i,j+1} - 4 \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j} \right) \right], \\ k_{2y;i,j} = \beta \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j} \right), \\ k_{2z;i,j} = x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j}, \\ \begin{cases} k_{3x;i,j} = \alpha \left[ -y_{i,j} \left( k \right) - \frac{h}{2} k_{2y;i,j} + \gamma \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{2x;i,j} \right) \right. \\ \left. - W \left( z_{i,j} \left( k \right) + \frac{h}{2} k_{2z;i,j} \right) \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{2x;i,j} \right) \right] \right. \\ \left. + D \left[ x_{i-1,j} \left( k \right) + \frac{h}{2} k_{2x;i-1,j} + x_{i+1,j} \left( k \right) \right. \\ \left. + \frac{h}{2} k_{2x;i+1,j} + x_{i,j-1} \left( k \right) + \frac{h}{2} k_{2x;i,j-1} + x_{i,j+1} \left( k \right) \right. \\ \left. + \frac{h}{2} k_{2x;i,j+1} - 4 \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{2x;i,j} \right) \right], \\ k_{3y;i,j} = \beta \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{2x;i,j} \right), \\ k_{3z;i,j} = x_{i,j} \left( k \right) + \frac{h}{2} k_{2x;i,j}, \end{cases}$$

$$k_{2y;i,j} = \beta \left( x_{i,j} \left( k \right) + \frac{h}{2} k_{1x;i,j} \right),\,$$

$$k_{2z;i,j} = x_{i,j}(k) + \frac{h}{2}k_{1x;i,j}$$

$$\begin{cases} k_{3x;i,j} = \alpha \left[ -y_{i,j}(k) - \frac{h}{2}k_{2y;i,j} + \gamma \left( x_{i,j}(k) + \frac{h}{2}k_{2x;i,j} \right) \right] \\ -W \left( z_{i,j}(k) + \frac{h}{2}k_{2z;i,j} \right) \left( x_{i,j}(k) + \frac{h}{2}k_{2x;i,j} \right) \right] \\ +D \left[ x_{i-1,j}(k) + \frac{h}{2}k_{2x;i-1,j} + x_{i+1,j}(k) + \frac{h}{2}k_{2x;i+1,j} + x_{i,j-1}(k) + \frac{h}{2}k_{2x;i,j-1} + x_{i,j+1}(k) + \frac{h}{2}k_{2x;i,j+1} - 4 \left( x_{i,j}(k) + \frac{h}{2}k_{2x;i,j} \right) \right], \end{cases}$$

$$k_{3y;i,j} = \beta \left( x_{i,j}(k) + \frac{h}{2} k_{2x;i,j} \right)$$

$$k_{3z;i,j} = x_{i,j}(k) + \frac{h}{2}k_{2x;i,j}$$

Memristive Cellular Neural/Nonlinear Networks

$$\begin{cases} k_{4x;i,j} = \alpha \left[ -y_{i,j} \left( k \right) - h k_{3y;i,j} + \gamma \left( x_{i,j} \left( k \right) + h k_{3x;i,j} \right) \right. \\ \left. - W \left( z_{i,j} \left( k \right) + h k_{3z;i,j} \right) \left( x_{i,j} \left( k \right) + h k_{3x;i,j} \right) \right] \\ \left. + D \left[ x_{i-1,j} \left( k \right) + h k_{3x;i-1,j} + x_{i+1,j} \left( k \right) \right. \\ \left. + h k_{3x;i+1,j} + x_{i,j-1} \left( k \right) + h k_{3x;i,j-1} + x_{i,j+1} \left( k \right) \right. \\ \left. + h k_{3x;i,j+1} - 4 \left( x_{i,j} \left( k \right) + h k_{3x;i,j} \right) \right], \end{cases}$$

$$k_{4y;i,j} = \beta \left( x_{i,j} \left( k \right) + h k_{3x;i,j} \right),$$

$$k_{4z;i,j} = x_{i,j} \left( k \right) + h k_{3x;i,j},$$

$$- 0.004 \text{ is an interval}$$

and h = 0.004 is an interval

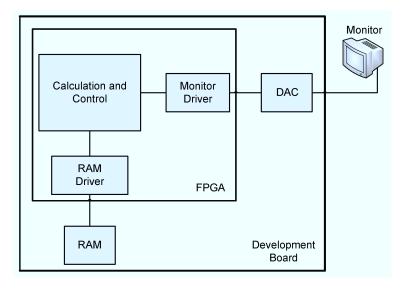

Using the model (4.9), MCNNs can be implemented in an FPGAbased system with the block diagram shown in Fig. 4.10. The core of system is the "calculation and control block" which computes the integration of Eqs. (4.9), displays the results on a monitor and controls the interface with the RAM memory.

Here, RAM memory is an IS42S16400 high-speed synchronous dynamic RAM. It is the external memory provided on the development board and is used to store the state variables data of the memristive cells.

#### 4.2.2 Experimental results

The whole system consists of an Altera DE2 development board and a monitor. DE2 board includes a Cyclone II EP2C35F672C6 FPGA chip in a 672-pin package and provides other hardware resources to connect to other external devices. The DE2 board is connected to the monitor

Fig. 4.10: Block diagram of the whole system based on an FPGA chip.

through a VGA DAC (10-bit high-speed triple DACs) with VGA-out connector. The calculation and control block, RAM driver block, and monitor driver block are programmed on FPGA chip with hardware description language VHDL. Firstly, the calculation and control block based on Altera's Nios II processor emulates MCNN by integrating Eqs. (4.9) for a time step. After that, the result is stored in the RAM and displayed on the monitor. The outputs of the FPGA system as shown in the monitor are then captured by a camera as reported in Figs. 4.11, 4.12, 4.13 and 4.14. These figures are intended to demonstrate that the generated waves have the main properties of the autowaves, namely an amplitude and shape of the wave that do not change during propagation, the absence of reflection or interference, and annihilation when two waves collides.

Fig. 4.11: Autowave propagation from the left–hand side to the right–hand side of the MCNN.

Fig. 4.12: Autowave formation starts from the centre of MCNN.

Fig. 4.13: Annihilation of two colliding autowaves.

Fig. 4.14: Annihilation of two colliding autowaves.

# Simple memristive time—delay chaotic systems

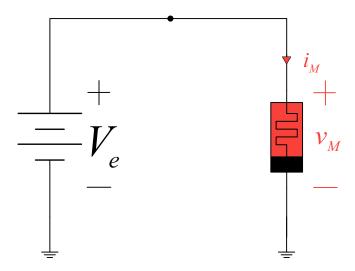

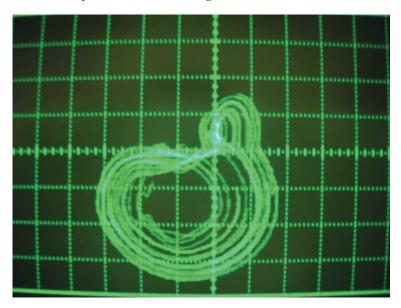

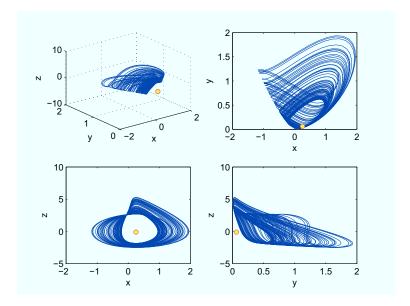

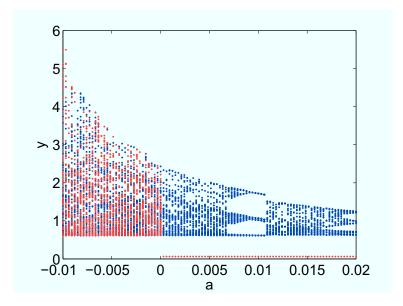

Memristive systems have appeared in various application fields from non-volatile memory devices and biological structures to chaotic circuits. In this chapter, we propose nonlinear circuits based on memristive systems with the presence of delay, i.e., memristive systems in which the state of the memristor depends on the time-delay. These systems can exhibit chaotic behaviour and, notably, in the second model, only a capacitor and a memristor are required to obtain chaos.

Chaotic circuits have been designed to confirm theoretical models [43] as well as to be used in diverse applications such as secure chaotic communications [34], robotics [8] or random generator implementation [121]. Chaotic circuits can be either autonomous or non–autonomous, and an actual issue on the research on chaotic is the design of chaotic circuit with the minimum number of elements. On one hand, some simple non–autonomous chaotic circuits were proposed. Linsay built an anharmonic oscillator with a resistor, an inductor, and a varactor diode [63]. Dean [36] presented a circuit with a capacitor, a linear resistor, and

a resistor including ohmic losses in the inductor winding. Chaos could occur in a sinusoidally driven second-order circuit made of three linear elements and a Chua's diode [58]. A non-autonomous chaotic circuit based on one transistor, two capacitors, and two resistors was described by Lindberg [62, 42]. On the other hand, in the realm of autonomous circuits, Chua's circuit has received a significant amount of attention [43]. The four-element Chua's circuit introduced in [10] can be considered as the simplest circuit of this kind. In addition, by using a nonlinear active memristor, a three-elements autonomous circuit has been realized [72]. Piper [80] introduced some simple autonomous chaotic circuits using only op-amps and linear time-invariant passive components. More recently, the autonomous Hartley's oscillator based on a junction field effect transistor (JFET) and a tapped coil has been implemented [104]. Hence, the authors have named it the simplest chaotic two-component circuit. However, it is notable that, when the Tchitnga's circuit is analyzed in terms of the concept of mathematical simplicity given [80], it is not really simple because of its four state equations.

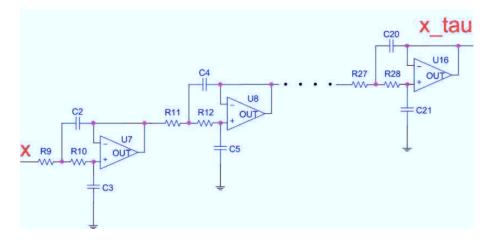

From another point of view, if the prospective study is to create a simple chaotic circuit described by few dynamical equations, it is clear that time–delayed systems are good candidates. Due to time–delay these systems are infinite–dimensional dynamical systems [118] and thus a system described by just one delay differential equation can be chaotic.

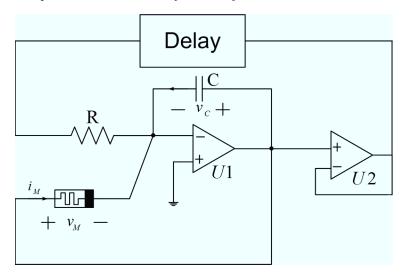

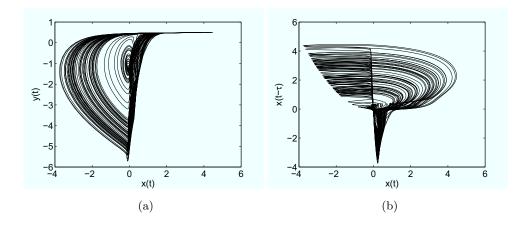

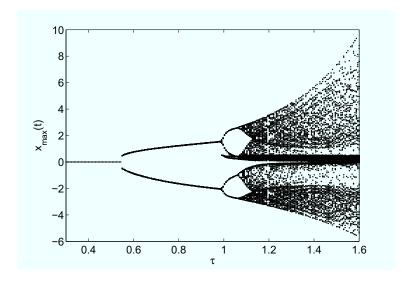

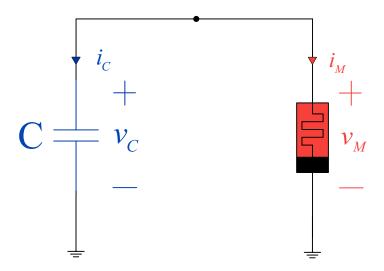

In this chapter, we investigate the possibility of designing memristive time–delay systems (MTDS) exhibiting chaotic behaviour. In particular, we introduce three different autonomous MTDS models and propose implementations of the second model which consists of just two components: a time-delay memristive element and a capacitor as well as the third model consisting of just one memristive element.

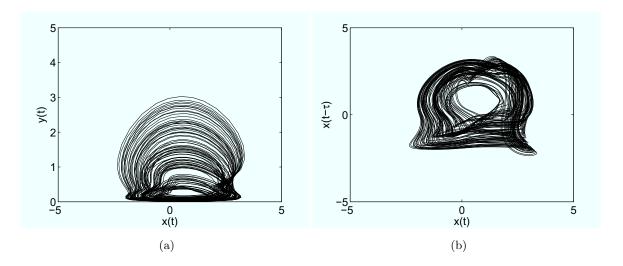

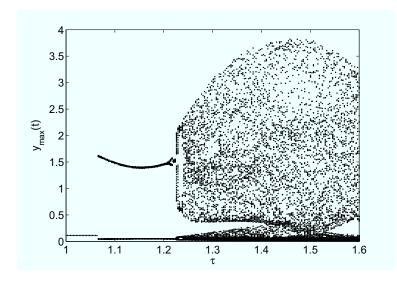

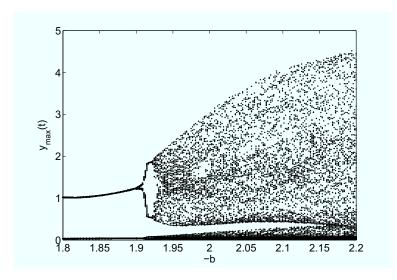

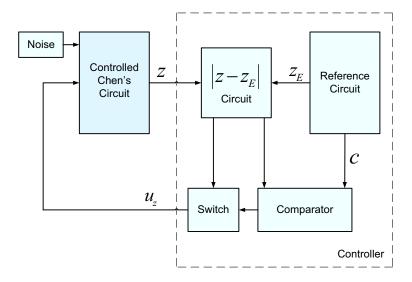

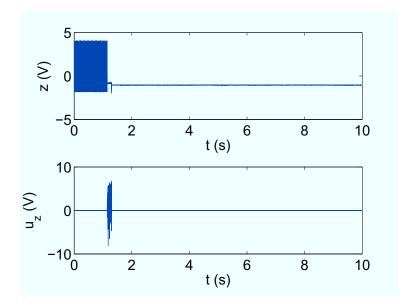

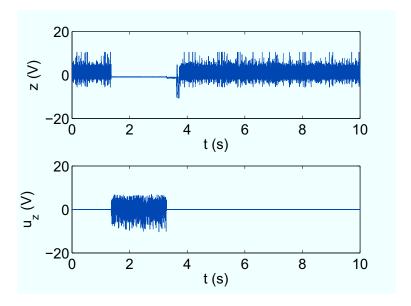

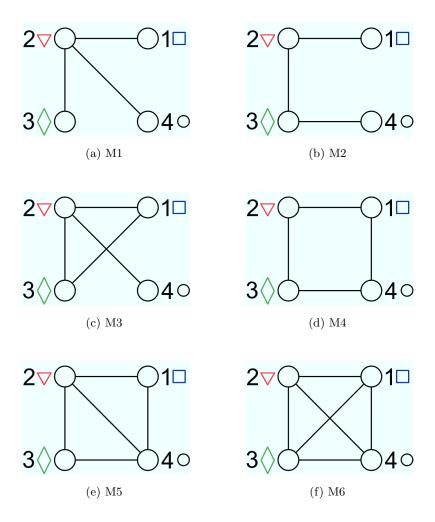

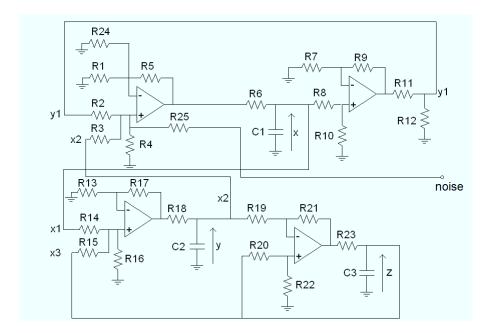

### 5.1 Models of memristive time-delay systems