### DIPARTIMENTO di INGEGNERIA ELETTRICA, ELETTRONICA e INFORMATICA

# Low Power Techniques for Future Network-on-Chip Architectures

A thesis submitted for the degree of Doctor of Philosophy in Ingegneria dei Sistemi, Energetica, Informatica e delle Telecomunicazioni XXIX Ciclo

> Author Andrea Mineo

Advisor: Chiar.mo Prof. Vincenzo Catania *Co-Advisors:* Chiar.mo Prof. Maurizio Palesi Chiar.mo Prof. Giuseppe Ascia

Coordinator: Chiar.mo Prof. Paolo Arena

October 2016

"A mia moglie, Adriana" "A mio nonno, Andrea" "A mia zia, Pina" "A mia madre, con affetto" "A mio Padre"

# Contents

| 1        | Introduction |                                                |    |  |

|----------|--------------|------------------------------------------------|----|--|

|          | 1.1          | The Network-on-Chip Design Paradigm            | 2  |  |

|          |              | 1.1.1 Power Consumption                        | 3  |  |

|          |              | 1.1.2 Scalability Issues                       | 4  |  |

|          | 1.2          | The Future of Wires                            | 5  |  |

|          | 1.3          | Scope and Contributions of the Thesis          | 8  |  |

|          | 1.4          | Organization of the Thesis                     | 9  |  |

| <b>2</b> | Dat          | a Encoding Techniques in NoC Architectures     | 11 |  |

|          | 2.1          | Link Energy Consumption                        | 11 |  |

|          | 2.2          | Low Power Coding                               | 13 |  |

|          | 2.3          | Duplicate Add Parity Code                      | 14 |  |

|          | 2.4          | DAP Codec                                      | 14 |  |

|          |              | 2.4.1 Voltage Swing Reduction                  | 14 |  |

|          |              | 2.4.2 DAP on a Network-on-Chip                 | 16 |  |

| 3        | Rel          | iability Aware Adaptive Voltage Swing Scaling  | 18 |  |

|          | 3.1          | Probabilistic CMOS Technology                  | 19 |  |

|          | 3.2          | The Idea at a Glance                           | 20 |  |

|          | 3.3          | Contribution                                   | 21 |  |

|          | 3.4          | Limitations and Applicability                  | 22 |  |

|          | 3.5          | Architectural and Microarchitectural Design    |    |  |

|          |              | 3.5.1 Reconfigurable Link with Duplication     | 23 |  |

|          |              | 3.5.2 Reconfigurable Link without Duplication  | 24 |  |

|          |              | 3.5.3 With Duplication vs. Without Duplication | 25 |  |

|          |              | 3.5.4 Impact on the IC Design Flow             | 27 |  |

|          |              | 3.5.5 Control Circuitry                        | 28 |  |

|          | 3.6 | Design | n Configurations                                  | 29 |

|----------|-----|--------|---------------------------------------------------|----|

|          | 3.7 | Synth  | esis Results                                      | 30 |

|          | 3.8 | Exper  | iments                                            | 34 |

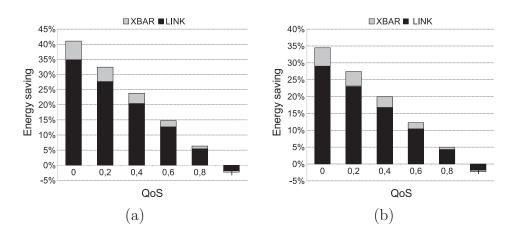

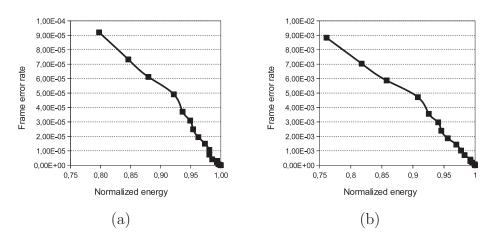

|          |     | 3.8.1  | Energy Saving $vs.$ QoS                           | 36 |

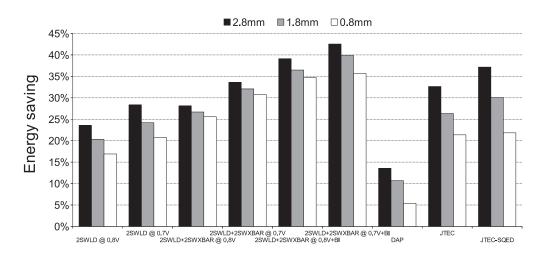

|          |     | 3.8.2  | Energy Saving vs. Link Length                     | 37 |

|          |     | 3.8.3  | Energy Saving vs. Packet Size                     | 38 |

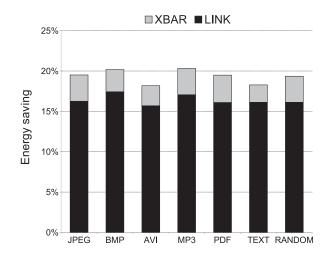

|          |     | 3.8.4  | Energy Saving vs. Different Data Types            | 38 |

|          |     | 3.8.5  | Energy Saving vs. Performance Degradation         | 39 |

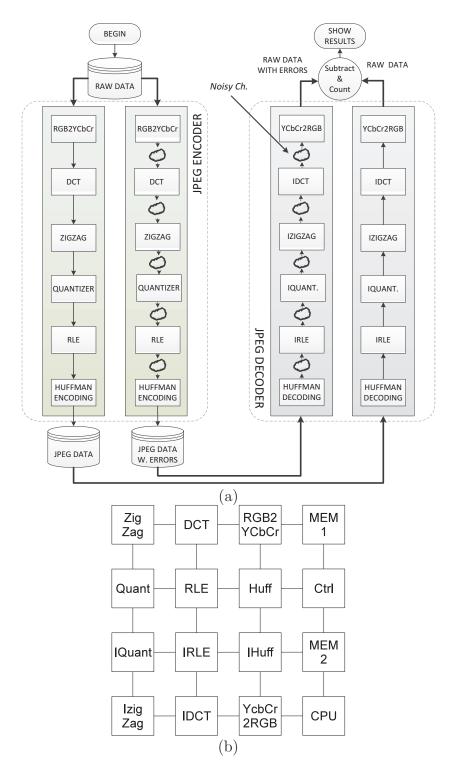

|          |     | 3.8.6  | Case Studies                                      | 40 |

|          | 3.9 | Concl  | usions                                            | 45 |

| 4        | Em  | erging | Network-on-Chip Paradigms                         | 48 |

|          | 4.1 | 3D No  | ${ m pc}$                                         | 48 |

|          |     | 4.1.1  | 3D Symmetric NoC                                  | 49 |

|          |     | 4.1.2  | 3D NoC-Bus Hybrid Architecture                    | 50 |

|          |     | 4.1.3  | Multi-layer 3D NoC Router Design                  | 51 |

|          | 4.2 | Photo  | nic NoCs                                          | 51 |

|          | 4.3 | Wirele | ess NoCs                                          | 52 |

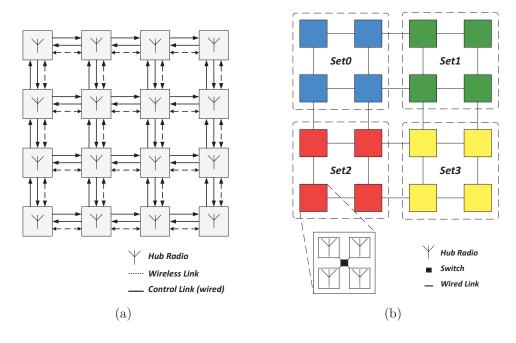

|          |     | 4.3.1  | Mesh-Topology Based WiNoCs                        | 54 |

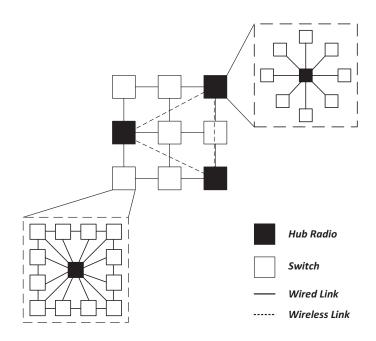

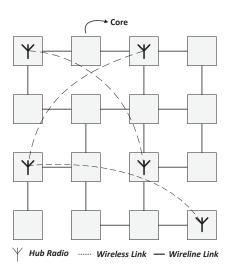

|          |     | 4.3.2  | Small-World Network Based WiNoCs                  | 55 |

|          |     | 4.3.3  | Physical Layer Management                         | 59 |

|          | 4.4 | Comp   | arative Analysis                                  | 62 |

| <b>5</b> | Tun | able 7 | Transmitting Power for WiNoC Architectures        | 63 |

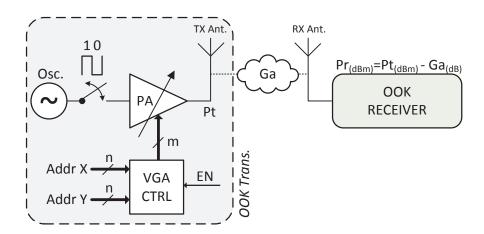

|          | 5.1 | Adapt  | tive Transmitting Power Transceiver               | 64 |

|          |     | 5.1.1  | Variable Gain Amplifier Controller                | 64 |

|          |     | 5.1.2  | Determining the Minimal Transmitting Power        | 65 |

|          |     | 5.1.3  | Overall Flow                                      | 68 |

|          |     | 5.1.4  | The Mapping Problem                               | 69 |

|          | 5.2 | Exper  | iments                                            | 71 |

|          |     | 5.2.1  | Bandwidth and Radiation Pattern                   | 72 |

|          |     | 5.2.2  | Attenuation Maps                                  | 73 |

|          |     | 5.2.3  | VGA Controller Analysis                           | 75 |

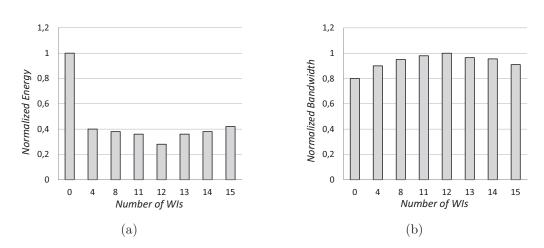

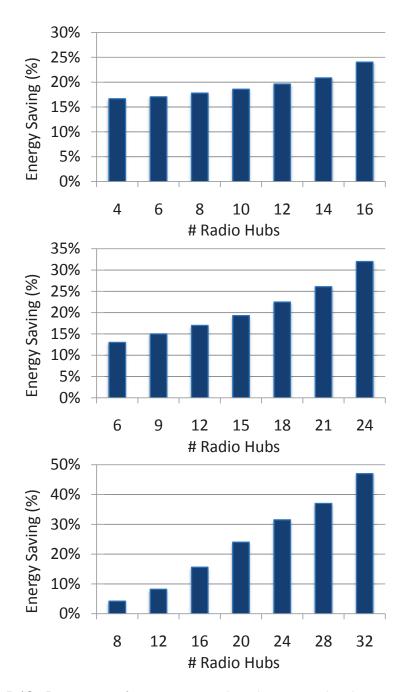

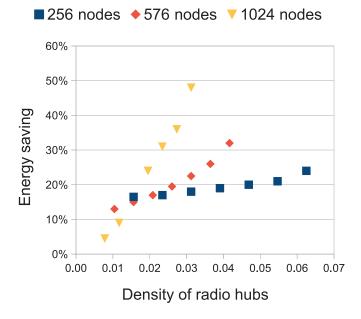

|          |     | 5.2.4  | Energy Saving in Mesh-Topology Based WiNoCs       | 78 |

|          |     | 5.2.5  | Energy Saving in Small-World Network Based WiNoCs | 81 |

|          |     | 5.2.6  | Application Mapping                               | 83 |

|          |     |        |                                                   |    |

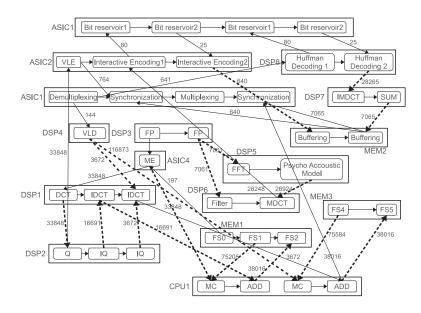

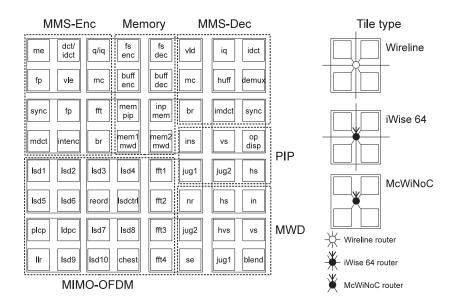

|                                             | 5.2.7                                                              | Case Study                                                                                                                                                                                                                                                                                                            | . 84                               |  |  |  |  |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|

| 5.3                                         | Conclu                                                             | isions                                                                                                                                                                                                                                                                                                                | . 84                               |  |  |  |  |  |  |  |

| Exploiting Antenna Directivity in WiNoCs 88 |                                                                    |                                                                                                                                                                                                                                                                                                                       |                                    |  |  |  |  |  |  |  |

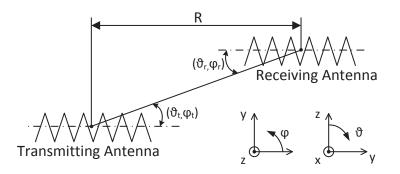

| 6.1                                         | Anteni                                                             | na Directivity Optimization                                                                                                                                                                                                                                                                                           | . 89                               |  |  |  |  |  |  |  |

|                                             | 6.1.1                                                              | Antenna Directivity                                                                                                                                                                                                                                                                                                   | . 89                               |  |  |  |  |  |  |  |

|                                             | 6.1.2                                                              | Formulation of the Problem                                                                                                                                                                                                                                                                                            | . 91                               |  |  |  |  |  |  |  |

|                                             | 6.1.3                                                              | General Design Flow                                                                                                                                                                                                                                                                                                   | . 92                               |  |  |  |  |  |  |  |

| 6.2                                         | Experi                                                             | imental Results                                                                                                                                                                                                                                                                                                       | . 93                               |  |  |  |  |  |  |  |

|                                             | 6.2.1                                                              | Simulation Methodology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                             | . 93                               |  |  |  |  |  |  |  |

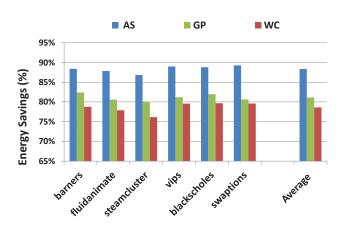

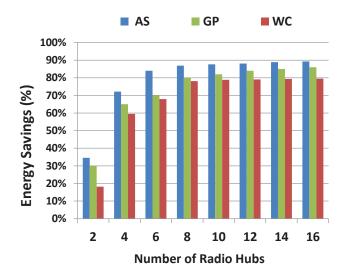

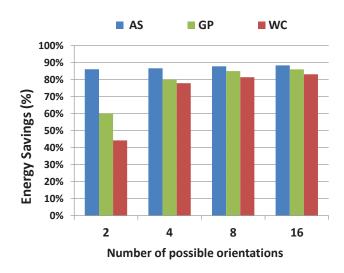

|                                             | 6.2.2                                                              | Energy Saving Analysis                                                                                                                                                                                                                                                                                                | . 95                               |  |  |  |  |  |  |  |

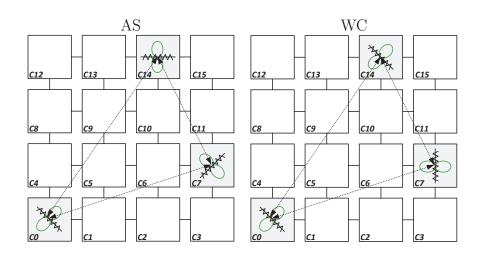

|                                             | 6.2.3                                                              | Case Study                                                                                                                                                                                                                                                                                                            | . 98                               |  |  |  |  |  |  |  |

| 6.3                                         | Conclu                                                             | isions                                                                                                                                                                                                                                                                                                                | . 99                               |  |  |  |  |  |  |  |

| Sma                                         | rt Tra                                                             | ansceiver for WiNoCs                                                                                                                                                                                                                                                                                                  | 101                                |  |  |  |  |  |  |  |

| 7.1                                         | Siest                                                              | A Power Reduction Strategy                                                                                                                                                                                                                                                                                            | . 102                              |  |  |  |  |  |  |  |

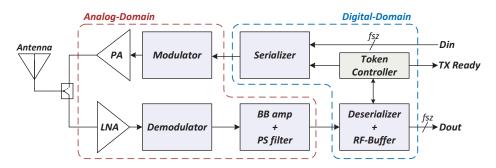

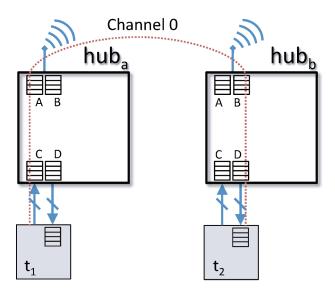

|                                             | 7.1.1                                                              | Radio-Hub Architecture Overview                                                                                                                                                                                                                                                                                       | . 102                              |  |  |  |  |  |  |  |

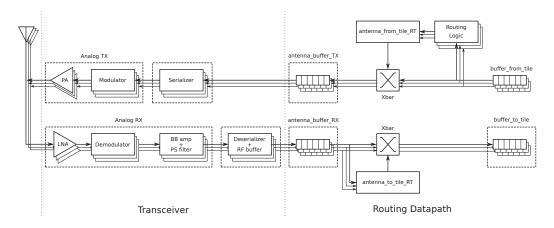

|                                             | 7.1.2                                                              | Radio-hub data flows                                                                                                                                                                                                                                                                                                  | . 104                              |  |  |  |  |  |  |  |

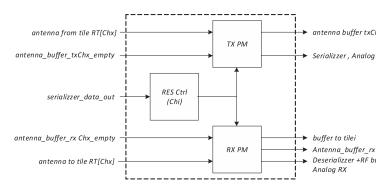

|                                             | 7.1.3                                                              | Detecting the Radio Event Sleep status                                                                                                                                                                                                                                                                                | . 105                              |  |  |  |  |  |  |  |

|                                             | 7.1.4                                                              | TX Power Management                                                                                                                                                                                                                                                                                                   | . 107                              |  |  |  |  |  |  |  |

|                                             | 7.1.5                                                              | RX Power Management                                                                                                                                                                                                                                                                                                   | . 108                              |  |  |  |  |  |  |  |

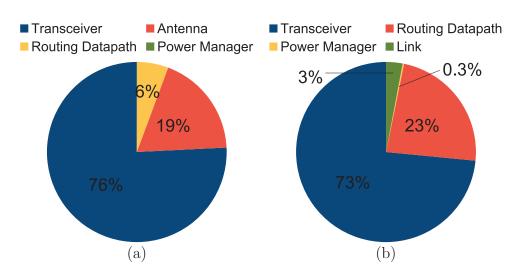

|                                             | 7.1.6                                                              | Hardware Implementation                                                                                                                                                                                                                                                                                               | . 109                              |  |  |  |  |  |  |  |

| 7.2                                         | Experi                                                             | iments                                                                                                                                                                                                                                                                                                                | . 111                              |  |  |  |  |  |  |  |

|                                             | 7.2.1                                                              | Simulation Setup                                                                                                                                                                                                                                                                                                      | . 111                              |  |  |  |  |  |  |  |

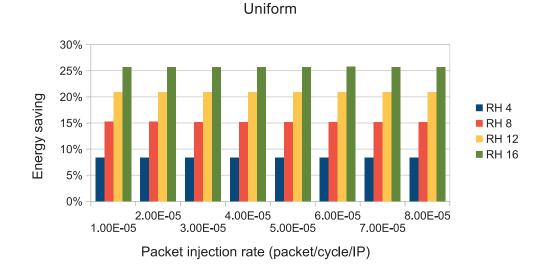

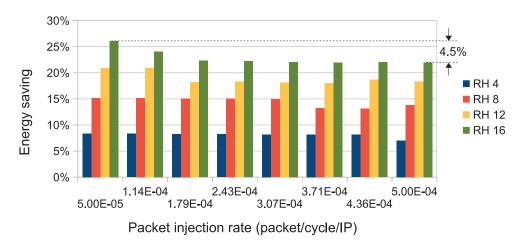

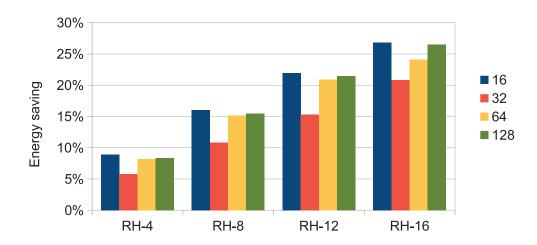

|                                             | 7.2.2                                                              | Effect of Packet Size and Packet Injection Rate                                                                                                                                                                                                                                                                       | . 113                              |  |  |  |  |  |  |  |

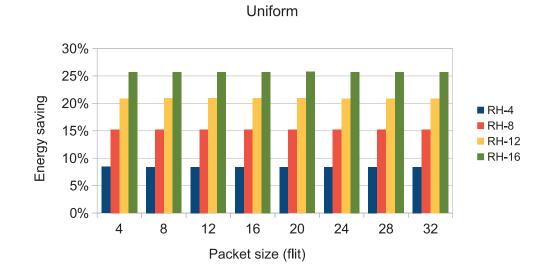

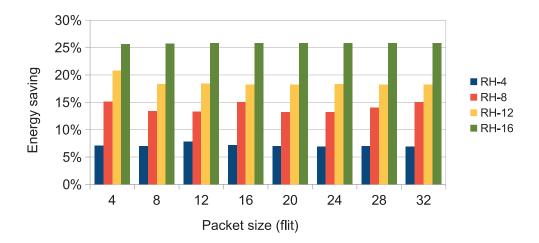

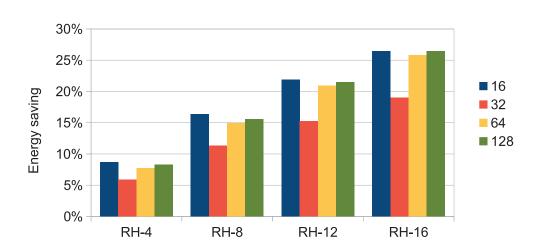

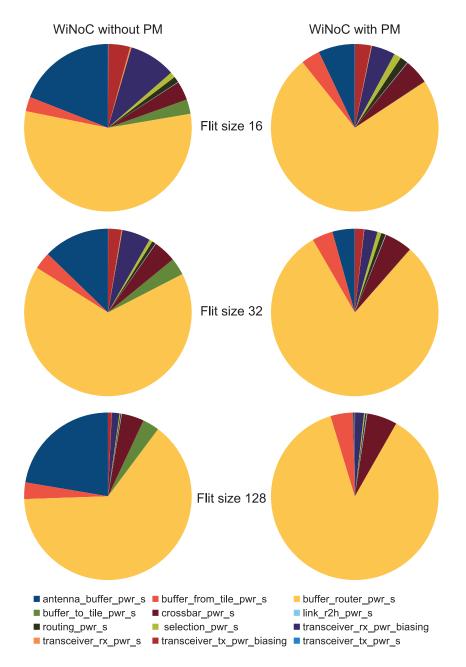

|                                             | 7.2.3                                                              | Effect of Flit Size                                                                                                                                                                                                                                                                                                   | . 117                              |  |  |  |  |  |  |  |

|                                             | 7.2.4                                                              | Effect of Buffers Size                                                                                                                                                                                                                                                                                                | . 121                              |  |  |  |  |  |  |  |

|                                             | 7.2.5                                                              | Wireless Communication Energy Saving                                                                                                                                                                                                                                                                                  | . 122                              |  |  |  |  |  |  |  |

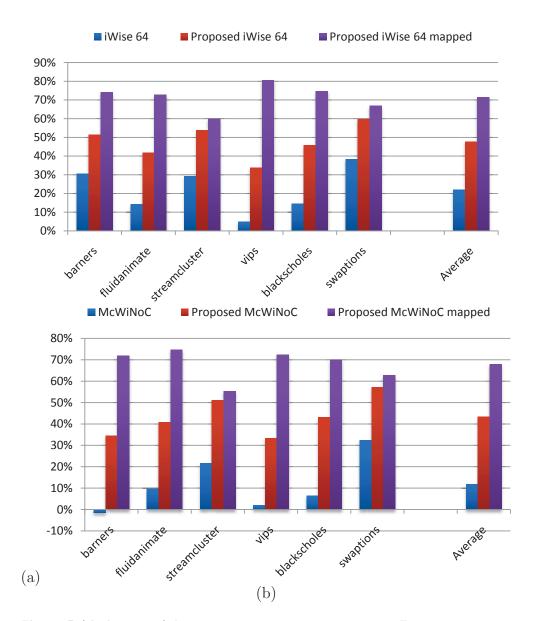

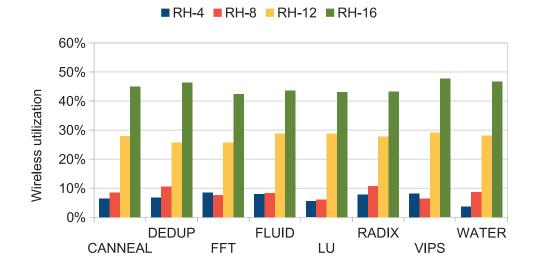

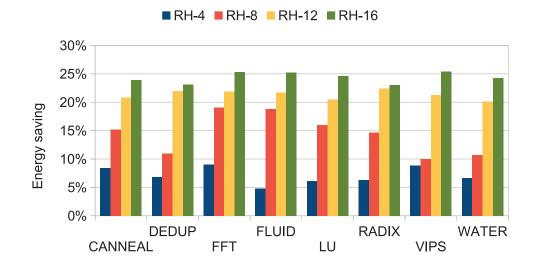

|                                             | 7.2.6                                                              | Assessment under Real Traffic Scenarios                                                                                                                                                                                                                                                                               | . 123                              |  |  |  |  |  |  |  |

| 7.3                                         | Conclu                                                             | isions                                                                                                                                                                                                                                                                                                                | . 124                              |  |  |  |  |  |  |  |

| Con                                         | clusior                                                            | a                                                                                                                                                                                                                                                                                                                     | 125                                |  |  |  |  |  |  |  |

| open                                        | dices                                                              |                                                                                                                                                                                                                                                                                                                       | 128                                |  |  |  |  |  |  |  |

| A Scientific Production                     |                                                                    |                                                                                                                                                                                                                                                                                                                       |                                    |  |  |  |  |  |  |  |

|                                             | Exp<br>6.1<br>6.2<br>6.3<br>5ma<br>7.1<br>7.2<br>7.2<br>7.3<br>Con | 5.3 Conclu<br>Exploiting<br>6.1 Anten:<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2 Experi<br>6.2.1<br>6.2.2<br>6.2.3<br>6.3 Conclu<br>Smart Tra<br>7.1 SiESTA<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.2 Experi<br>7.2.1<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.3 Conclusion<br>opendices | <ul> <li>5.3 Conclusions</li></ul> |  |  |  |  |  |  |  |

## Abstract

In a multi-many/core system, the Network-on-Chip (NoC) based communication backbone is responsible for a relevant fraction of the overall energy budget. In fact, the I/O buffers, the crossbars of the routers and the inter-router links are the main contributors of the NoC's energy dissipation. Specifically, electrical links will soon represent a bottleneck both in terms of energy dissipation and delay. For these reasons, several short and long terms solutions have been proposed from the NoCs research community. In particular, several techniques are based on reducing the voltage swing in links resulting in significant energy saving. Unfortunately, as voltage swing reduces, the bit-error-rate increases, that in turn compromises the communication reliability. Within this context, starting from the assumption that not all the communications need same level of reliability, in this dissertation we propose techniques and architectures for run-time tuning of the voltage swing of inter-router links. The proposed technique, is compared with the state of the art in link energy reduction through data encoding under both synthetic and real traffic scenarios. We found that the proposed techniques allow to significantly reduce the energy consumption of the NoC fabric without degrading the performance metrics. Energy savings ranging from 20%to 43% have been observed without any relevant impact on the performance metrics.

Since proposed short terms solutions will not longer satisfy the ever more aggressive energy consumption constraints, especially when the number of integrated processing elements (PEs) will be over the thousandths (as predicted by ITRS) new emerging paradigms have been proposed. In particular, wireless networks-on-chip (WiNoCs), have been recently proposed as candidate solutions for addressing the scalability limitations of conventional multi-hop NoC architectures. In a WiNoC, a subset of network nodes, namely, radio hubs, are equipped with a wireless interface that allows them to wire-

#### CONTENTS

lessly communicate with other radio hubs. Thus, long-range communications, which would involve multiple hops in a conventional wireline NoC, can be realized by a single hop through the radio medium. Unfortunately, the energy consumed by the RF transceiver into the radio hub (i.e., the main building block in a WiNoC), and in particular by its transmitter, accounts for a significant fraction of the overall communication energy. In order to alleviate such contribution, two techniques have been proposed in this thesis. A first solution consists in a runtime tunable transmitting power technique for improving the energy efficiency of the transceiver. The basic idea is tuning the transmitting power based on the physical location of the recipient of the current communication. Specifically, based on the destination address of the incoming packet, the radio hub tunes its transmitting power to a minimum level, but high enough to reach the destination antenna without exceeding a certain bit error ratio. The proposed technique applied on different representative WiNoC architectures results in an average transmitter energy reduction up to 50% without any impact on performance and with a negligible overhead in terms of silicon area. A second solution focuses on the impact of antennas orientation on energy figures and performs a design space exploration for determining the optimal orientation of the antennas in such a way to minimize the communication energy consumption. When the antennas are optimally oriented, up to 80% transmitter energy saving has been observed.

Unfortunately, energy consumed by WiNoC transceiver does not depend by the transmitter but also by other modules including the receiver. In this sense, in order to obtain a further energy reduction in this thesis we propose a technique based on selectively turning off, for the appropriate number of cycles, all the radio-hubs that are not involved in the current wireless communication. The proposed energy managing technique is assessed on several network configurations under different traffic scenarios both synthetic and extracted from the execution of real applications. The obtained results show that, the application of the proposed technique allows up to 25% total communication energy saving without any impact on performance and with a negligible impact on the silicon area of the radio-hub.

# Chapter 1

# Introduction

Moore's Law<sup>1</sup> has powered mainstream microelectronics for the past decades promising lower costs, lower power consumption and higher performance in terms of computational speed. Following the same trend, modern applications such as high performance computing, mobile computing and applications related to the Internet of Things (IoT), require higher and higher performance especially in terms of speed and energy efficiency. Unfortunately, in the ultra-deep sub-micron (UDSM) era, power and integration density in CMOS technologies do not scale at the same pace. In fact, as integration density increases by 2x every two years, power efficiency increases by only 1.4x. This trend is known as the end of Dennard's Scaling or as the begin of the *dark silicon* era [93]. The latter means that, mainly due to power dissipation issues, modern Systems-on-Chip (SoCs) cannot be anymore designed for operating at the maximum frequency while exploiting the entire chip resources at the same time. For facing such disruptive trend, in the last decade modern System-on-Chip are migrating from a single core (operating at high frequency) to a multicore architecture (with a lower operating frequency). In fact, nowadays, modern SoCs integrate ever more intellectual properties/processing (IPs/PEs) on the same chip. Following this trend, several chip makers, including Intel, AMD and TILERA, have already released commercial multi/many-core products. For instance, AMD has recently released the first native eight core processor for the desktop market [9], while TILERA and Intel have released a 72-core and a 60-core coprocessors, respec-

$<sup>^1\</sup>mathrm{Moore's}$  Law predicted that the number of transistors on a chip doubles every 18 to 24 months

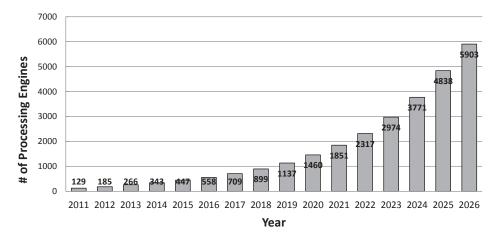

**Figure 1.1:** Number of integrated processing elements inside a System-on-Chip [4].

tively [94, 23]. On the research side, Intel developed two prototypes in [98] and [21]. The former, developed in 2008, integrates 80 processing cores in a 65 nm CMOS technology, while the latter, after 6 years, integrates 256 cores in an 22 nm Tri-Gate CMOS technology. Fig. 1.1, reports a forecast on the number of integrated PEs over years showing quite clearly that such number is expected to reach the thousand within the 2020.

## 1.1 The Network-on-Chip Design Paradigm

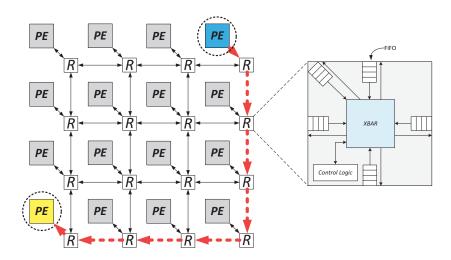

Although the potential computational capabilities of many-core systems improve as the number of cores increases, on the other hand the on-chip communication subsystem becomes the actual bottleneck for what it concerns scalability, energy efficiency, performance and reliability of the entire system. The Network-on-Chip (NoC) design paradigm [12] is currently considered as the most viable solution for sustaining the communication demand of modern many-core architectures and for addressing the technological challenges in UDSM silicon nodes. As depicted in Fig. 1.2 a NoC is constituted by several processing elements (PEs) connected by a switched packet network made of switches (or routers) and electrical point-to-point links. Into the network, packets are fragmented in several small data units named *flits* which are stored and routed (according to a routing algorithm) by means of the main element of a NoC, namely, router. Due to severe timing constraints,

Figure 1.2: A 2D-Mesh NoC.

the latter must implements several pipeline stages. For this reason, each flit is routed through the network in a multi-hop fashion. In the picture mentioned above, for instance, a processing element (in blue) requires 7 hops to send a flit to the yellow PE.

#### 1.1.1 Power Consumption

During the past years, several NoC architectures have been proposed by performing extensive design-space exploration involving topologies, routing algorithms, switching techniques, micro-architectural parameters, etc. From these studies it has been established that, although in the past the computation and the memory subsystems were considered as the main responsible of energy consumption, in NoC-based multi/many-core architectures the communication subsystem accounts for a relevant fraction of the overall energy budget. For instance, in the Intel's 80-tiles TeraFLOPS processor [98], the communication power (due to routers and links) accounts for about 30% of the total power. Experimental results in [37] shown that the contribution of the interconnection network to the total power ranges from 15% (8-core tiled CMP) to 35% (16-core tiled CMP) on average, with some applications reaching up to 50%. In the AEthereal NoC the largest percentage of power dissipation (54%) is due to the NoC clock, followed by the NoC links (18%) [88]. In [33], it has been shown that on-chip interconnects account for a significant fraction (up to 50%) of the total on-chip energy consumption.

Figure 1.3: Router's power breackdown [98].

Entering in more details, the power dissipated by a NoC depends on both physical wires and router internal components. As depicted in Fig. 1.2, the latter is essentially constituted by several FIFO (First In, First Out) memories to store incoming flits, a control logic and by a crossbar which is in charge of routing packets to a specific output port. In order to understand how the power is distributed into a router, Fig. 1.3 shows, for instance, the power breakdown of the Intel TeraFLOPS [98]. From this graph is clear that power consumption is dominated by FIFOs (22%), crossbar (15%) and electrical links (17%). For this reason, the power consumption of a router could be simplified as follows:

$$P = P_{fifo} + P_{xbar} + P_{link}.$$

(1.1)

From Eqn. (1.1) results clear now that, for the sake of power minimization a NoC designer should act on such three contributions. As it will be seen in the rest of the thesis, our research is mainly focused on such techniques or emerging NoC paradigms that try to optimize both delay and power metrics on physical links which are a bottleneck for today's and future NoC based SoCs.

#### 1.1.2 Scalability Issues

In the NoC context is better thinking in terms of energy consumption rather than power dissipation. Starting from Eqn. (1.1) we can express the energy consumed to transfer a piece of information (a flit) in function of the number hops of the route between the source and the destination node:

$$E_{flit} = n \cdot (E_{fifo} + E_{xbar} + E_{link}) = n \cdot E_{router} + n \cdot E_{link}$$

(1.2)

where n is the number of routers and links crossed during a transfer between a source and destination node. The worst case happens when the number of hops equals to the network diameter (based on the position of source and destination). Considering the network depicted in Fig. 1.2 it results trivial computing the network diameter D as reported in the Eqn. 1.3.

$$D = 2 \cdot (\sqrt{N} - 1). \tag{1.3}$$

Since the latter depends by the number of integrated processing elements N, worst case energy can be finally computed as follows:

$$max(E_{flit}) = D \cdot E_{hop} = 2 \cdot (\sqrt{N} - 1) \cdot E_{hop}.$$

(1.4)

From this last result emerges that when the number of cores increase energy consumed to transfer data from distant PEs increases as well.

The same behavior is valide for latency too. Due to pipeline structure of a router we can also compute latency in terms of the network diameter Dand the number of pipeline stages  $N_{pipeline}$  as follows:

$$max(Latency) = N_{pipeline} \cdot D = 2N_{pipeline} \cdot (\sqrt{N} - 1)$$

(1.5)

If we consider, for instance, a 3 pipeline stages router and 100 cores the worst case latency results in 54 cycles. Thus, following the ITRS predictions as reported early, it results clear that around 2020 both latency and energy consumption will be a real issue for future NoC-based SoCs.

#### 1.2 The Future of Wires

In this section we would to show how metallic/dielectrical wires will be a bottleneck, especially in terms of delay. In order to better understand this phenomena, a simple model to compute parasitics effects will be exposed. As it will be seen, different effects emerging in future technologies make metallic wires the weak point of today's NoC base systems.

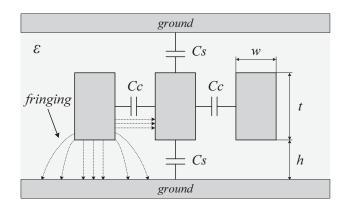

In NoC-based SoCs, each point-to-point link consists of a bus made of n wires, where n is equal to the size of a flit. In fact, such flits are transmitted over the network in a parallel fashion through dedicated buses. Metallic wires are further arranged with minimal spacing in order to save area. Since in digital integrated circuits both delay and power consumption are proportional

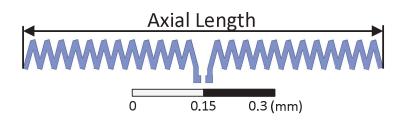

Figure 1.4: Stripline Model.

to parasitic capacitances introduced by devices and electrical wires [81, 44], it is useful to know how to compute distributed capacitance form technological parameters. From electromagnetic theory, to compute such parasitics in CMOS metal/dielectric wires, a strip-line model should be used [69]. Fig. 1.4 shows a model of a generic bit-line inside a bus in which capacitance is thus modeled by four parallel-plate capacitors for the top, bottom, right, and left sides, plus a constant term for fringing capacitance. In modern technologies, vertical and horizontal capacitors may have different relative dielectrics using low-k materials.

The "far" plates for the top and bottom capacitors are typically modeled as being grounded, since they represent a collection of orthogonally routed conductors that, averaged over the length of the wire, maintain a constant voltage. Capacitors to the left and right, on the other hand, have datadependent effective capacitances that can vary: if the left and right neighbors switch in the opposite direction as the wire, the effective sidewall capacitances double, and if they switch with the wire, the effective sidewall capacitances approach zero. This effect is known as "Miller multiplication". These left and right neighbors are also the worst offenders for noise injection. The fringe term depends weakly on geometry and for today's technologies is about 40 f F/mm. For the very top layers of metal with no upper layers, we can use three parallel plates with extra fringing terms on the two horizontal capacitors.

In order to estimate the capacitance per unit length we can thus write:

$$c_{dist} = \epsilon_0 \epsilon \left( 2K \frac{t}{spacing} + 2\epsilon \frac{w}{h} \right) + fringe(\epsilon)$$

(1.6)

Where,  $\epsilon_d$  is the dielectric constant assumed to be homogeneously distributed both between layers and between metal lines within a layer,  $\epsilon_0$  is the permit of free space, K takes in accounts of the Miller multiplication (varying from 0 to 2), while t, w and h are geometrical parameters as shown in Fig. 1.4.

A convenient simple model, enough for first-order hand calculation can be derived from the above equation by means of the following assumptions:

- The interlevel dielectric thickness h is assumed to be the same as the metal thickness t.

- Intralevel dielectric thickness and wire width w is assumed to be half of the pitch (spacing + w).

- An average dielectric constant value is used for the case where a range of values is suggested in the roadmap for a given technology node.

- The capacitance values represent the worst switching scenario when two adjacent wires, on the same level, are simultaneously switching in the apposite direction as the signal line, hence doubling the intralevel capacitance contribution.

The former computed capacitance per unit length is thus given by Eqn. 1.7.

$$c_{dist} = 2\epsilon_d \epsilon_0 \left(\frac{1+2AR^2}{AR}\right) + fringe(\epsilon)$$

(1.7)

where AR is the aspect ratio of the wire defined as the thickness to width ratio of the metal. The introduction of such constant is particularly useful to understand the capacitances trend for future technology steps.

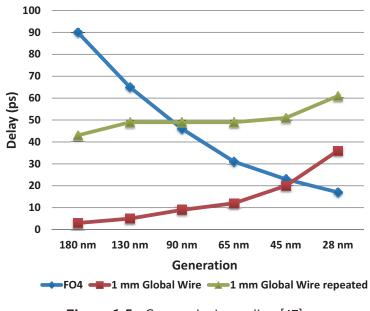

In fact, ITRS [3] predicts that aspect ratio is destined to increase, and thus, from Eqn. 1.7 is clear that in the UDSM regime parasitics introduced by wires id destined to increase too. Consequently, as technology shrinks, the ratio between the wire capacitance and input gate capacitance increases [47] making the interconnection network the principal actor with respect to the energy/power metric. This particular aspect can be also viewed in terms of delay. In fact, as shown in Fig. 1.5, for each technology step delay due to logical gate (in terms of FO4) decreases while wire delay increases even with repeaters insertion. It means that, for future technologies the wire

Figure 1.5: Gate and wire scaling [47].

contribution will be the real bottleneck both in terms of speed and energy efficiency.

#### **1.3** Scope and Contributions of the Thesis

For facing scalability problems discussed before, several solutions have been proposed in literature. In particular, in this dissertation, we aim to minimize the negative impact in terms of energy consumption of a NoC by proposing both short and long term solutions. The research presented here falls in two topics on minimizing energy in modern NoC based systems: data encoding techniques and an emerging interconnect paradigm named Wireless Networks-on-Chip (WiNoCs). While the former represents a short term solution the latter are based on new technologies beyond traditional CMOS processes. Both topics and related proposed solutions will be briefly introduced in the rest of this section.

1. Data Encoding Techniques in Network-on-Chip architectures. According with these techniques, energy consumption could be minimized by reducing possible responsible of power consumption such as the switching activity or voltage swing in physical lines. In this thesis it is proposed a technique for minimizing the energy consumption by reducing voltage swing. Unfortunately, reducing the voltage swing has a negative impact on the signal integrity (i.e., on the content of the packets traveling in the NoC) which results in a reduction of the communication reliability due to the increase of the bit-error-rate (BER). As for the computation counterpart in which the concept of probabilistic CMOS has been recently investigated, [71], we believe that, in the context of communication, it is not always necessary to ensure that the BER must be the same for all the transmitted packets. Based on this, we propose to extend the general concept of probabilistic CMOS to the communication side of a NoC based system. In particular, the concept is applied to two of the main components of a NoC architecture which mostly affect the NoC energy, namely, links and crossbar. We present link architectures able to be configured on-line for working at two different voltage swings, namely, full and low-voltage swing. The basic assumption is that not all the communications involved in an application have the same reliability requirements. Thus, the links and the crossbars traversed by the packets of a communication which does not have stringent reliability requirements are configured on the fly to work at low-swing voltage.

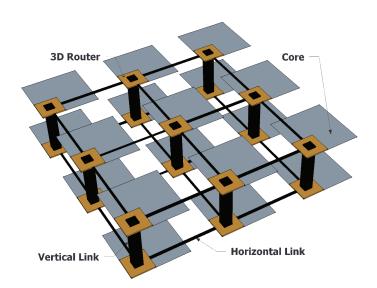

2. Emerging interconnect technologies for on-chip networks. To face with the scalability problems especially in terms of latency, new technologies such as 3D NoC, optical and wireless NoC (WiNoC) are emerging as technological alternatives to the wire based NoCs [15]. In particular a WiNoC constituted a wireless backbone upon the traditional wire-based NoC [30]. WiNoCs Introduce new hardware structures such as antenna and transceivers that represent an overhead in terms of area and power. In this dissertation we present three techniques for reducing power consumption on the transceiver which is the most power hungry device of this kind of systems.

## 1.4 Organization of the Thesis

The remainder of the thesis is as follows. Before detailing the different contributions of our work, Chapter 2 and 4 introduce some concepts of Data Encoding Techniques and of emerging technology respectively. Chapter 3 exposes a data encoding technique which reduces energy by varying, at runtime, the voltage swing on physical lines.

Chapter 5, 6 and 7 describe three proposed technique, developed for Wireless Network-on-Chip paradigm. In particular as it will be seen, transceiver power consumption is predominant if compared to other WiNoC devices. Proposed techniques thus work on the reduction of such power. To do this, the technique exposed in the Chapter 5 reduces energy by varying the transmitting power of transmitter based on the position of source and destination. Technique proposed in the Chapter 6 provides a design flow to determine the optimum orientation of antennas in a WiNoC. Further, in the Chapter 7 we propose a mechanism to reduce energy consumption when a receiver is not a recipient of a message. Finally, Chapter 8 concludes the dissertation.

## Chapter 2

# Data Encoding Techniques in Network-on-Chip Architectures

As stated before, in this dissertation we will expose a method for reducing energy consumption due to physical lines of a NoC. To better understand the proposed technique, we start to show how to compute power dissipation on electrical wires. After that a background has been given, the proposed scheme will be finally discussed in the next chapter.

#### 2.1 Link Energy Consumption

The average switching energy dissipated by a digital circuit can be estimated using the following formula [81]:

$$E_{dyn} = \alpha \cdot C_L \cdot V_{dd}^2, \tag{2.1}$$

where  $\alpha$  is the switching activity of the nodes of the circuit,  $C_L$  is the total load capacitance, and  $V_{dd}$  is the supply voltage. From Eqn. 2.1 it can be observed that  $V_{dd}$  has a squared effect on the dynamic energy consumption.

A physical line can be seen as a distributed load for a driving gate. However, for the sake of power estimation, it can be assumed as a lumped load [81]:

$$C_L = c_l \cdot L,$$

where  $c_l$  is the the capacitance per unit length that can be computed as in the Eqn. 1.7 (pp. 7), and L is the line length.

**Table 2.1:** Effective capacitance,  $C_{eff}$ , for each type of transition on a victim and aggressors lines [80]. The  $\uparrow$  and  $\downarrow$  represents the versus of transition and the symbol '-' is used for representing no transition in the specified line.

| $C_{eff}$                                              | Transition Pattern                                                                                                                                                                                                                  | p             |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| $C_s$                                                  | $(\uparrow,\uparrow,\uparrow)$ $(\downarrow,\downarrow,\downarrow)$                                                                                                                                                                 | 0             |

| $\begin{array}{c} C_s + C_c \\ C_s + 2C_c \end{array}$ | $ \begin{array}{c} (-,\uparrow,\uparrow) (-,\downarrow,\downarrow) (\uparrow,\uparrow,-) (\downarrow,\downarrow,-) \\ (-,\uparrow,-) (-,\downarrow,-) (\downarrow,\uparrow,\uparrow) (\downarrow,\downarrow,\uparrow) \end{array} $ | $\frac{1}{2}$ |

| $C_s + 3C_c$                                           | $ \begin{array}{c} (\uparrow,\uparrow,\downarrow) (\uparrow,\downarrow,\downarrow) \\ (-,\uparrow,\downarrow) (-,\downarrow,\uparrow) (\uparrow,\downarrow,-) (\downarrow,\uparrow,-) \end{array} $                                 | 3             |

| $\ddot{C_s} + 4\ddot{C_c}$                             | $(\uparrow,\downarrow,\uparrow)$ $(\downarrow,\uparrow,\downarrow)$                                                                                                                                                                 | 4             |

For the physical lines, the average power dissipation also depends on the type of transition that occur on the current line and in the neighboring lines (contribution due to the crosstalk). Specifically, in terms of energy consumption, the Eqn. (2.1) can be written as follow:

$$E_{dyn} = C_{eff} \cdot V_{dd}^2, \tag{2.2}$$

where  $C_{eff}$  is the effective capacitance that not only depends on the transition in the current line, but also by the specific transition of the aggressor line.  $C_{eff}$  is often expressed as:

$$C_{eff} = C_s + p \cdot C_c, \tag{2.3}$$

where  $C_s$  is the line's self capacitance, and  $C_c$  is the coupling capacitance. The factor p can be 0, 1, 2, 3, or 4 according to Tab. 2.1. The elements in the table are 3-tuples in which the central term represents the victim line (*i.e.*, the line under examination) while the left and the right terms represent the neighboring aggressor lines. If present, the arrow indicates the transition type ( $\uparrow$  rising transition,  $\downarrow$  falling transition). The symbol "—" represents the case in which no transition occurs in the current line. It should be pointed out that, if the victim line makes a transition while the neighboring lines remain steady (*i.e.*, (-,  $\uparrow$ , -) or (-,  $\downarrow$ , -)), the effective capacitance is  $C_s + 2C_c$ , but from the noise point of view, there is not injection of charge in the victim line.

### 2.2 Low Power Coding

From previous section results clear that for reducing energy due to electrical wires (disposed in a bus fashion), a designer can acts on three main constituting factors: by reducing the switching activity ( $\alpha$  term), reducing effective capacitance ( $C_{eff}$ ) or decreasing the voltage swing. For alleviating these terms, data that should be transmitted on a bus can be coded properly. Initially proposed for shared bus based System-on-Chips (SoCs), several coding techniques have been developed by research community [86]. In particular, we can distinguish among three main coding families:

- Low Power Coding (LPC): the power dissipation in the bus depends on data transition activity ( $\alpha$ ). This kind of techniques try to reduce such activity. Their effectiveness are relevant only when coupling capacitance between lines are negligible. Interesting research papers that fall in this topic can be found in [87, 72].

- Crosstalk Avoidance Coding (CAC): both power dissipation and delay of a wire in a bus depend to it's transitions and to adjacent wires activity. From Eqn. 2.3, the worst-case delay of a wire is when p term is equal to 4. The purpose of the crosstalk avoidance coding is to limit such term to 2. This goal can be achieved if some transitions are forbidden by mean of a dedicated codec [77].

- Joint Crosstalk Avoidance and Forward Error Correction (CAC+FEC): a joint crosstalk avoidance and error-correction code can be obtained by combining a crosstalk avoidance code with an error- correcting code. *p* term is reduced from 4 to 2 and voltage swing can be scaled down by means of an error correction code.

Since in the UDSM regime coupling capacitance has a higher impact, both CAC and CAC+FEC techniques are more effective in terms of obtained energy saving if compared to low power codes. Further, from recent studies [42] results that CAC+FEC techniques are the best candidate for saving energy especially in the NoC context. Since the data encoding technique proposed in this thesis will be compared with several CAC+FEC techniques, a represative scheme named Duplicate Add Parity, will be described in the next section.

## 2.3 Duplicate Add Parity Code

As mentioned in the in the previous section, CAC techniques obtain an energy reduction by avoiding critical transitions on two adjacent physical lines. The technique *Duplicate Add Parity* obtain such requisite by doubling each bitline of a bus. In this way, for each line, we have the original data and a copy of it. It should be noted that added lines act as shielding lines from the original data that should be transmitted on the bus. Furthermore, an error detection mechanism is introduced to detect transmission errors by mean of a parity bit. With this technique, an n bits of data become coded in a 2n + 1 bits. Since line have been duplicated, with the introduction of such mechanism, if an error occurs on a specific bit-line, a copy of this data can be selected. The just gained robustness can be therefore exploited to scale down the voltage swing on the lines. Thus, according with the Eqn. 2.1 a squared effects on energy reduction will be achieved.

### 2.4 DAP Codec

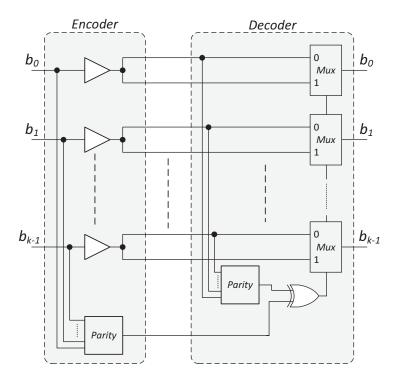

Logical scheme of the codec which implements the DAP technique on a n bit bus is shown in Fig. 2.1. The encoder is constituted by a combinational block name *Parity*. The former computes the logical XOR between each bit-line as follows:

$$Parity = b_0 \oplus b_1 \oplus \ldots b_{k-1}$$

With the introduction of additional line coming from this block, the number of bits 1 on the bus should be even for any words combinations. The decoder is thus implemented with the *Parity* block followed by a logical XOR which driver the selector of a series of multiplexers. Therefore, if an error occurs into the bus, the decoder will selects the right lane selected as data valid.

#### 2.4.1 Voltage Swing Reduction

As mentioned before, the introduction of a error detection mechanism is translated in a higher robustness. The probability that an error occurs on a single bite, named BER (Bit Error Rate), is strictly tied to the signal to

Figure 2.1: CAC+ECC (DAP) Codec.

noise ration presents on the line. Thus, to an higher voltage swing follows an higher errors immunity. The probability  $\epsilon$  that a single error happens on a line (BER) can modeled as follows:

$$\epsilon = Q\left(\frac{V_{dd}}{2\sigma_N^2}\right) \tag{2.4}$$

where Q is a well known equation (Eqn. 5.4).

$$Q(x) = \frac{1}{\sqrt{2\pi}} \int_{x}^{\infty} e^{-\frac{y^2}{2}} dy$$

(2.5)

The probability of having an error on a word is a function of the BER for each single bit-line ( $\epsilon$ ). If we refer with  $P_{\text{unc}}(\epsilon)$  the BER without any implemented error correction mechanism and with  $P_{\text{ecc}}(\epsilon)$  the BER obtained after that coding is applied, we will have:

$$P_{\rm ecc}(\epsilon) \le P_{\rm unc}(\epsilon) \tag{2.6}$$

or using the Eqn. 2.4 and by fixing  $P_{\rm ecc}(\epsilon) = P_{\rm unc}(\epsilon)$ , we can reduce the voltage swing as reported below.

$$\widehat{V_{dd}} = V_{dd} \frac{Q^{-1}(\hat{\epsilon})}{Q^{-1}(\epsilon)} \tag{2.7}$$

In the Eqn. 2.7,  $V_{dd}$  represents the nominal voltage without any correction while  $\widehat{V_{dd}}$  is a reduce swing that can achieve the same BER by means of the error corrections mechanism.

Without any correction the probability that an error occurs in to a word is tied to the  $\epsilon$  as reported below:

$$P_{\rm unc}(\epsilon) = k\epsilon \tag{2.8}$$

where k represent the number of bits presents on the word. If DAP strategy is applied, residual error probability can be computed like in [77] (reported in the Eqn. 2.9).

$$P_{\text{DAP}}(\epsilon) = 1 - \sum_{i=0}^{k} \binom{k}{i} \epsilon^{i} (1-\epsilon)^{2k-1+i} - \sum_{i=0}^{k/2} \binom{2k+1}{2i+1} \epsilon^{2i+1} (1-\epsilon)^{2k-2i}$$

(2.9)

The latter could be simplify only wor small  $\epsilon$  values as reported in the Eqn. 2.10.

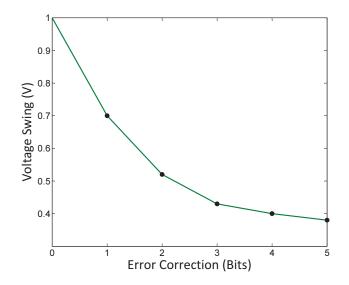

In literature are present other techniques to reduce voltage swing further by detecting more than just one error. In Fig. 2.2 is reported the voltage swing as function of the number of detected error.

$$P_{\rm DAP}(\epsilon) = \frac{3k(k+1)}{2}\epsilon^2 \tag{2.10}$$

#### 2.4.2 DAP on a Network-on-Chip

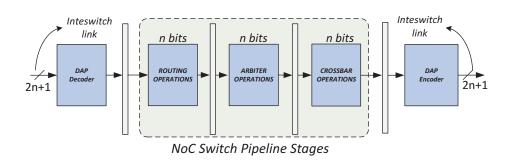

As discussed on previous sections, applying a DAP codec on a bus the voltage swing could be reduced. Since a NoC is constituted by point-to-point links, a encoder and decoder pair should be instantiated for each oh them. From this, it results clear that the price to pays for implementing such technique will be both in terms of silicon area and latency. In Fig.2.3 is depicted DAP codec on a traditional NoC switch. By adding the DAP codec, tho more pipeline stages ha been added. For facing the latency issue in the next section we propose a technique that reduces voltage on the lines without affects the pipeline structure of a router. As it will be seen, a trade-off between latency and bit error rate (BER) will be introduced.

Figure 2.2: DAP: Voltage swing with a BER of  $10^{-20}$  following Eqn. 2.7 with  $\sigma = 65$  mV.

**Figure 2.3:** DAP codec implemented in a NoC router. Two pipeline stages have been added.

## Chapter 3

# Reliability Aware Adaptive Voltage Swing Scaling

As mentioned in the previous section, state-of-art data encoding techniques (such as DAP technique) are based on voltage reduction that can be obtained by mean of an error detection mechanism. Such techniques are, in fact, based on a sequence of actions that can be summarized as follows:

- 1. Decrease the link voltage swing.

- 2. The BER increases.

- 3. Encode data and/or use an error correction scheme.

- 4. The BER decreases to the nominal value (*i.e.*, that observed at nominal voltage swing).

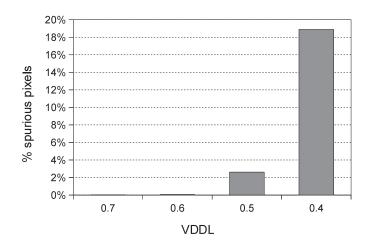

Since performing operation described at the point 3 leads to a penalty both in terms of additional silicon area and delay (as shown in Sec. 2.4.2), in the research presented here we propose a techniques that stops at the point 2. We, in fact, start from the assumption that for some specific communications, a higher BER can be tolerated without the need of using any error detection/correction mechanism because the possible data corruption does not affect the functionality of the application but only the quality of its results. For instance, suppose a packet whose payload is a macroblock of a frame in a video application. Even if the macroblock reaches its destination affected by errors, it results in a degradation of the image quality (*e.g.*, presence of spurious pixels in the image) but it does not affect the functionality of the algorithm that will process (use) the macroblock. Basically, the proposed technique exploits the trade-off between energy saving and communication reliability. Such communication reliability, in practical cases, results in a quality/accuracy/precision metric based on the underlying application. Conversely, data encoding techniques do not consider such trade-off. In fact, for them, all the communications must provide the same nominal BER and the maximum quality/accuracy/precision metric is assumed.

It should be pointed that, proposed idea is not new at all. In fact, on the the low reliability level in USDM CMOS devices (very susceptible to the process variation and to the perturbations due to the noise) has been recently exploited in the area of *probabilistic CMOS* for defining interesting trade-off between reliability and energy consumption [71].

Proposed technique tries to extend the general concept of probabilistic CMOS, which has been traditionally investigated in the context of computation, to the communication side of a NoC based SoC. Specifically, we present link architectures able to be configured on-line for working at two different voltage swings, namely, full and low-voltage swing. Thus, the links traversed by the packets of a communication which does not have stringent reliability requirements are configured on the fly to work at low-swing voltage. Conversely, if a communication has an higher constraint in terms of required BER, electrical links will be configured to work at the nominal voltage.

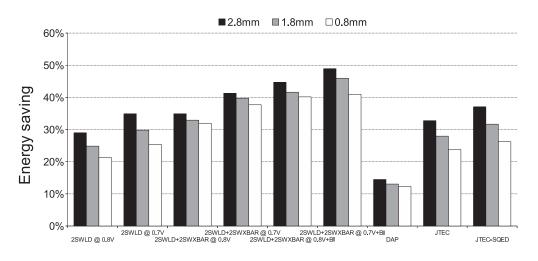

Experiments carried out on both synthetic and real traffic scenarios show the effectiveness of the proposed technique in terms of energy saving. Differently from the state-of-the-art in link energy reduction through data encoding schemes, which have a negative impact on the communication latency, the proposed technique provides higher energy saving without impacting the performance metrics.

### 3.1 Probabilistic CMOS Technology

In the UDSM era the device scaling faces several hurdles. Such devices are more and more susceptible to the process variation and to the perturbations due to the noise. For this reason, in [71] the authors introduced the concept of the *probabilistic CMOS* devices or PCMOS for short. Introducing the probabilistic devices, the ordinary boolean functions has been substituting with the probabilistic switching function in which the output results are not deterministic but have a given probability of correctness p to obtain the ordinary operations.

Principles of statistical thermodynamics may be applied to such devices to quantify their energy consumption. While a deterministic switch consumes at least  $KT \ln(2)$  (with T the temperature and K the Boltzmann constant) Joule of energy, a probabilistic switch can realize a switching functions with  $KT \ln(2p)$  Joule of energy [8]. As in the standard static-CMOS circuitry the energy consumption depends by the supply voltage, several research works [71, 8] use the voltage scaling to obtain a squared reduction of energy consumption introducing a tradeoff with the operation's correctness [70]. In fact, the introduction of the concept of probabilistic CMOS allows to split the applications domain in applications which can tolerate the probabilistic behavior (such as multimedia applications) and applications that can even benefit (or harness) from probabilistic behavior at the devices level naturally such as Bayesian inference [55], Probabilistic Cellular Automata [39], and Hyper Encryption [31]. Interested reader in [46] can find more recent developments in this research field. For the best of our knowledge, the concept of probabilistic CMOS has been exploited only for the computation. In the research presented here, we want to exploit the modularity and the flexibility of the NoC design paradigm for extending the concept of probabilistic CMOS to the communication side of the system.

#### **3.2** The Idea at a Glance

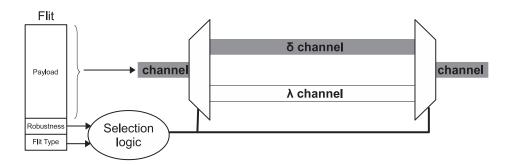

The basic idea of the proposed technique can be summarized as follows. Let us suppose that the communication system makes it available two different kinds of communication channels, namely, the *default* ( $\delta$ ) channels and the *low power* ( $\lambda$ ) channels. A  $\delta$  channel uses the nominal voltage swing whereas a  $\lambda$  channel uses a lower voltage swing. The flits of the packets of communications travel on  $\delta$  channels as usual. However, the flits of the packets of communications which do not have stringent reliability requirements, will use the  $\lambda$  channels with a consequent reduction of energy consumption.

The implementation of this mechanism requires just a single bit of infor-

Figure 3.1: General scheme implementing the proposed idea.

mation to be stored in the head flit of the packet, namely, the robustness flag (R). When R is set, all the flits of the packet will use only  $\delta$  channels, whereas when R is not set, the body flits of the packet will use the  $\lambda$  channel (Fig. 3.1). It should be pointed out that, head flits are always transmitted on  $\delta$  channels. This is because head flits carry critical information (*e.g.*, destination address) that cannot tolerate errors.

A general way for modeling at high level of abstraction an application to be mapped on a multicore SoC is by means of its communication graph (CG). A CG is a graph whose vertices represent the tasks and edges represent the communications. The edges of the CG are usually annotated with attributes which characterize that communications. Typical attributes are the average communication bandwidth and the traffic volume. In this research, we assume that the edges of the CG are annotated with an additional information, namely, the *robustness*. With the term robustness of a communication, c, we indicate the chance for c to be not affected by communication errors. Precisely, we consider two robustness levels denoted as *low* and *high*. A communication with a robustness *low* admits that the BER is higher than the nominal case. Conversely, a communication with a robustness flag of the packets belonging to a communication is set in accordance with the robustness attribute of that communication.

#### **3.3** Contribution

Reducing the voltage swing of NoC links is not a new technique in the context of energy efficient NoC design. However, the contribution of our proposed technique is not simply the selective reduction of voltage swing of NoC links. Differently from the previous approaches (chapter 2), the NoC link voltage swing is not only selective but also dynamic. That is, the voltage swing of a link is dynamically tuned based on the nature of the packets currently transmitted.

For the best of our knowledge, all the reviewed proposals in the context of NoC link energy reduction which exploit the possibility of reducing the voltage swing with a consequent trade-off in terms of reliability differ from the proposed scheme for an important and essential point. All the proposal discussed in the previous section assume that data transmitted through the NoC must be delivered to the destination cores unaffected by any error. Conversely, our contribution exploits the concepts of probabilistic CMOS in which there could be circumstances for which receiving data affected by errors does not have any impact on the functionalities of the system but they only affect some quality indexes that sometimes can be tolerated (e.g., imageor audio quality in a multimedia application). Based on this, the state-ofthe-art in data encoding makes use of error detection/correction mechanisms to guarantee a certain reliability level (usually expressed in terms of a maximum allowed BER) whereas our approach does not make use of any error detection/correction mechanism with a consequent reduction of complexity, cost, power and performance as it will be shown in the experimental section (Sec. 3.8).

### **3.4** Limitations and Applicability

The proposed scheme, to be used, needs the availability of a communication graph annotated with reliability information. Although for some applications it might be simple determining the reliability level of a certain communication, in general cases it is not a trivial task. In this research we do not address the important issue on how to map the communications involved in an application as reliable or unreliable. Such important issue is left for future work. The goal of our work is providing a mechanism which enables the user (*i.e.*, the application developer) to improve the energy efficiency of the application whenever he/she is able to classify the communications determined by the application as reliable or unreliable.

Further, it is assumed that the software communication library provides a new send primitive which exposes an additional parameter that allows to specify the reliability level of the current transfer. For instance, we assume the availability of a send primitive like send(dst, data, robustness). The robustness parameter is a boolean value that allows the programmer to specify whether the data transmitted to dst will use a reliable but power hungry links or an unreliable but low power links. In fact, the robustness flag is simply mapped into the robustness bit of the packet.

## 3.5 Architectural and Microarchitectural Design

The proposed technique discussed in the previous section is now elaborated and several implementations are analyzed. First we describe two runtime reconfigurable link architectures. In the first implementation, the  $\delta$  and  $\lambda$ channels are mapped into two different physical links, namely, the  $\delta$  and the  $\lambda$  links which work at nominal and low voltage swing, respectively. The overhead due to the duplication of the physical links of the first implementation is overcome by the second implementation in which a single physical link is used for both  $\delta$  and  $\lambda$  channels.

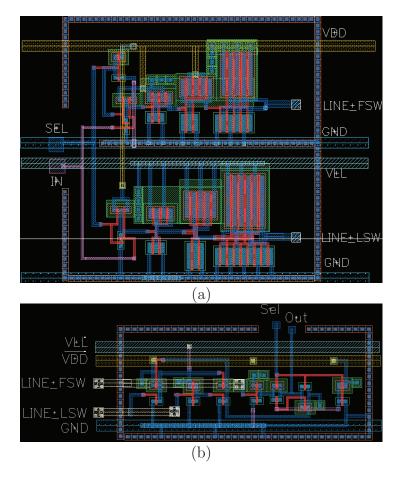

## 3.5.1 Runtime Reconfigurable Link Architecture with Duplication

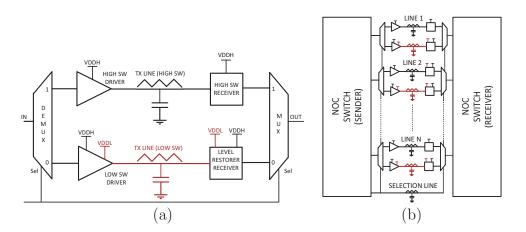

The proposed link architecture is shown in Fig. 3.2. The transceiver for the single bitline [Fig. 3.2(a)] is formed by two lines working at high voltage swing ( $\delta$ ) and low voltage swing ( $\lambda$ ), respectively. A demultiplexer (demux) is used to transmit the current bit over the  $\delta$  line or  $\lambda$  line based on a selection command stored in the head flit. Several techniques can be used to implement the low swing driver [107]. The low swing signal has to be converted back to a high swing signal before entering into the multiplexer (mux). Such conversion is performed by the module denoted as *level restorer* [107] in the figure.

Fig. 3.2(b) shows the proposed link architecture. As it can be observed, the  $\delta$  and  $\lambda$  lines are interleaved. Such organization provides an additional

Figure 3.2: Link architecture with line duplication. Bitline (a), link (b).

positive effect due to the fact that, in a given clock cycle, if  $\delta$  lines are active,  $\lambda$  lines are inactive and viceversa (with the term *active lines* we mean the lines currently involved in a transfer). It means that, an active line will have two neighboring inactive lines. Such inactive lines can be seen as a shield for the current line. That is, there is no switching in the neighboring lines causing p = 2 in Eqn. (2.3). In addition, such organization, can increase the throughput of the line due to the fact that the Miller multiplication [47] is avoided. Also, it results in less noisy links since crosstalk effects are reduced.

It should be pointed out that, the proposed circuitry remains valid even when the insertion of repeaters becomes necessary. In such case, the repeaters of the  $\delta$  and  $\lambda$  lines will be supplied with the nominal and low voltage, respectively.

## 3.5.2 Runtime Reconfigurable Link Architecture without Duplication

Although the link architecture discussed in the previous subsection has the advantage of i) reducing the crosstalk effects and ii) reducing the factor p in Eqn. (2.3) to 2, it has the drawback of duplicating the bit lines. Let us now present another link organization which does not require bit lines duplication.

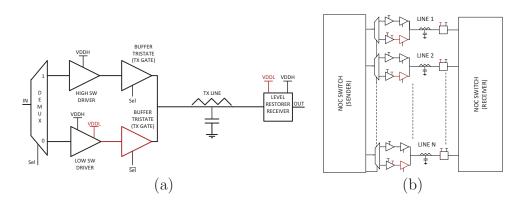

The scheme of the single link architecture is shown in Fig. 3.3(a). As it can be observed, the bitline is preceded by a chain formed by a demultiplexer, two tapered buffers as line drivers and two tristate buffers. The low swing conversion can be situated within the demultiplexer or in the tapered buffer

Figure 3.3: Link architecture without line duplication. Bitline (a), link (b).

as in one of many solutions proposed in [107]. Note that, if the demultiplexer is well sized, the introduction of a new stage not only does not affect the delay, but instead has a positive effect on performance if the proper number of inverter stages that compose the tapered buffer is chosen [89]. The tristate buffers are based on transmission gate logic. With this solution, if the select input is high (low), the full (low) swing path is active and the low (high) swing path is disconnected by the high impedance state introduced by tristate buffer. The level restorer circuit is similar to the sense amplifier used in RAM memories. It restores the signal at full swing if the signal on the line is set to low swing, or maintain the original swing if the signal is in full swing mode. In particular, when designing the level restorer, the logic threshold has to be set at half of low swing. In many cases, if the level restorer is well optimized, the speed of the circuits will be improved. Several circuital solutions for the design of the level restorer can be found in [107].

# 3.5.3 Runtime Reconfigurable Link Architecture: With Duplication vs. Without Duplication

In the previous two subsections, two runtime reconfigurable link architectures, namely, with duplication and without duplication, have been presented. In this subsection, we compare them in qualitative terms for what it concerns their impact on delay, area, and energy. A quantitative analysis is provided in the experimental section (Sec. 3.8).

• *Delay.* The duplication of the bitlines in the link avoids the occurrence of the the Miller multiplication which impacts the effective capacitance.

Thus, as it will be shown in the experiments, bitlines duplication allows to reduce the transmission delay. In addition, the absence of the Miller effect alleviates the crosstalk noise contribution with a consequent improvement in terms of communication robustness.

- Link Area. The link architecture without duplication reduces the wires congestion. With regard to the silicon area usage, bitlines use the higher metalization layers so as it is possible to route them over functional modules without using dedicated area for them [75]. However for long links which need the insertion of repeaters along the bitlines, since they use the same type of resources as other functional blocks, the area overhead of the repeaters should be taken into account and the use of the link architecture with duplication is preferred.

- Energy As it will be shown in the experimental results, the two link architectures exhibit similar average energy consumption for the same low voltage value used by the  $\delta$  line. This can be simply explained by comparing their effective capacitance as it determine the average energy consumption. In the link architecture with duplication, the effective capacitance is  $C_{eff} = C_s + 2C_c$  (Sec. 2.1, pp. 11). On the other side, in the link architecture without duplication, all the cases listed in Tab. 2.1 are possible. Now, considering a uniform random switching probability, the average number of switching type will be for p = 2. For this reason, even for the link architecture without duplication, on average, the effective capacitance is  $C_{eff} = C_s + 2C_c$ .

Overall, the two link architectures mainly differ in terms of delay and area. With regard to the delay, the link architecture with duplication exposes the minimal delay. In terms of area, the link architecture with duplication is significantly better than that with duplication especially when there is the need of repeaters along the bitlines. In terms of energy, the two link architectures perform almost the same for the same low voltage link level. For this reason, in the rest of this chapter, we do not distinguish between the two link architectures when energy saving results are presented.

#### 3.5.4 Impact on the IC Design Flow

In the previous sections, proposed architectures have been discussed from an architectural point of view. Since switch line driver could be implemented by using both semi-custom or fully automated design flow, results now mandatory to clarify how designers can manage the physical implementation of proposed schemes.

- Semi-custom Design Flow. In order to optimize power, area and delay metrics is common in the digital flow to implement some components such as high performance adders, RAMs, PLLs, I/O pads, and so on by mean of both hard macros and standard cells. In fact, the insertion of this custom building blocks inside the automated design flow in not trivial in conjunction with existing physical implementation tools [14, 90]. In particular, a NoC platform can be optimized by using customized crossbars, FIFO RAMs and line drivers. Since regulars NoCs present well controlled parasitic contribution, proposed line drivers could be designed once (one time effort) for a given technology and a given number of integrated IPs. As said still valid for crossbars.

- Fully Automated Flow. In several cases, in order to speed up design phase, is recommended a fully automated implementation by mean of standard cells based flow. Several Process Design Kit provides standard cell that can operate whit different operating voltages. During the physical implementation, several power domain can be specified by specifying such voltage. Different power domain can communicate together by mean of level shifter. For these reasons, proposed architectures can be implemented by using level shifters (used to implement level restorer) before/after line drivers, tristate buffer. It should be noted that, in the case of the architecture whit duplicated lines, repeater insertion does not implement level shifter. In this case low voltage bit-lines should be inserted inside actual power domain. Furthermore, since level shifter are usually implemented by transmission gate logic, several input/output operating voltage can be implemented. Further, in practical case, since standard cell are well characterized for different operating corners (PVT), when a low level path not is involved in an aggressive voltage scaling, the same standard-cell library can be

Figure 3.4: Finite State Machine implementing the selection logic in Fig. 3.2.

reused for both high an low voltage. Du to delay degradation such scenario is suitable only when crossbar and lines i not part of the router critical path.

To avoid any ambiguity, if not otherwise specified, a full custom implementation of line drivers and crossbar have been considered in the rest of this chapter.

#### 3.5.5 Control Circuitry

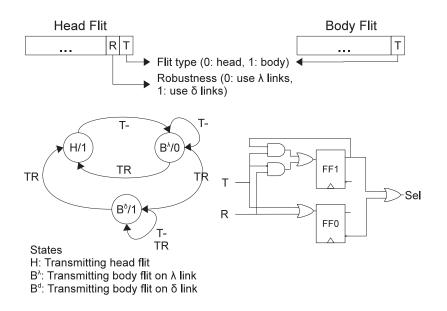

The selection logic for driving the selection signal in Figs. 3.2 and 3.3 can be implemented by means of a simple finite state machine (FSM) as shown in Fig. 3.4. We assume that the head flit provides a T bit which defines the flit type (either head or body), and a R bit which defines the robustness of the current communication. A body flit, does not have the R bit but only the T bit. As it can be observed, head flits (T = 0) determine Sel = 1irrespectively of the value of bt R. Body flits determine Sel = 1 (Sel = 0) if the R bit in the previously transmitted head flit was R = 1 (R = 0).

Figure 3.5: Design configurations.

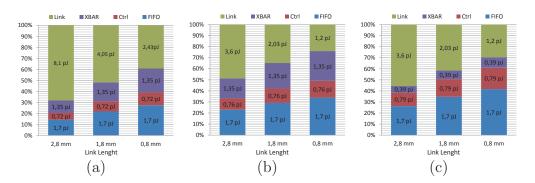

# **3.6** Design Configurations

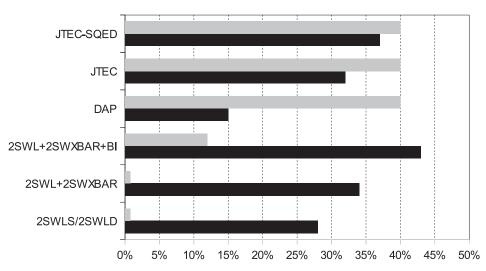

Concepts introduced for links could be used also for the routers crossbar. In fact, the latter is essentially composed by several wires driven by large multiplexers. A squared effects on power reduction could be also obtained, not only for wires but also in to the router in order to obtain an higher energy saving. Since applying proposed technique to the crossbar is a naive extension of structure already presented for links, we will not enter in detail to the circuital implementation of a modified crossbar, but we prefer the same, to provide several possible configurations obtained by mixing links organizations discussed so far with other that can be obtained applying the scheme to the crossbar. Such configurations are characterized by a different trade-off between performance, power, reliability, and area. Specifically, the configurations that will be analyzed in the experimental section are shown in Fig. 3.5 and are introduced in the following.

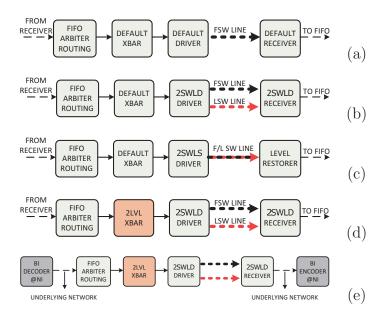

Baseline [Fig. 3.5(a)]: A traditional transceiver modeled with a chain of inverters as driver and a single inverter as receiver. This is the baseline scenario and represents the standard implementation in a traditional digital design flow when there is no need for the insertion of repeaters. Within the router a conventional crossbar is used.

- 2SWLD [Fig. 3.5(b)]: The proposed link transceiver with lines duplication presented in Sec. 3.5.1. Within the router a conventional crossbar is used.

- 3. 2SWLS [Fig. 3.5(c)]: The proposed link transceiver without duplication presented in Sec. 3.5.2. Here the shielding property obtained with the duplication is absent, but the link area is reduced.

- 4. 2SWL+2SWXBAR [Fig. 3.5(d)]: Like the 2SWLD configuration in which the two swing signaling is enabled in the crossbar.

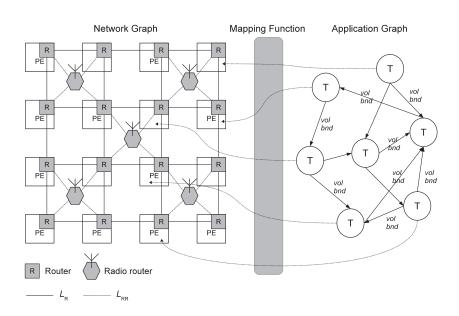

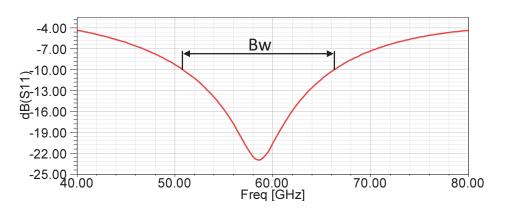

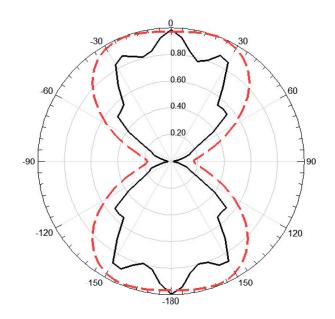

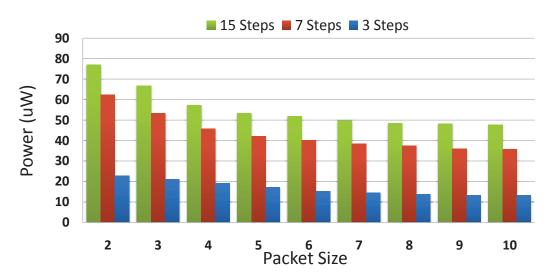

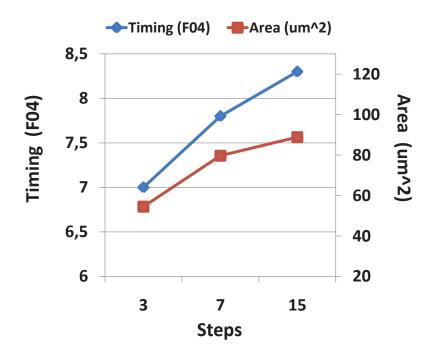

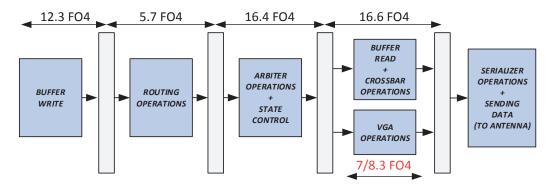

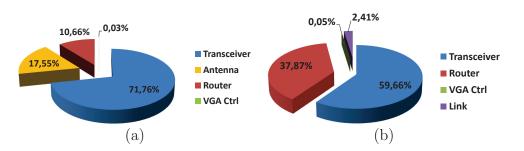

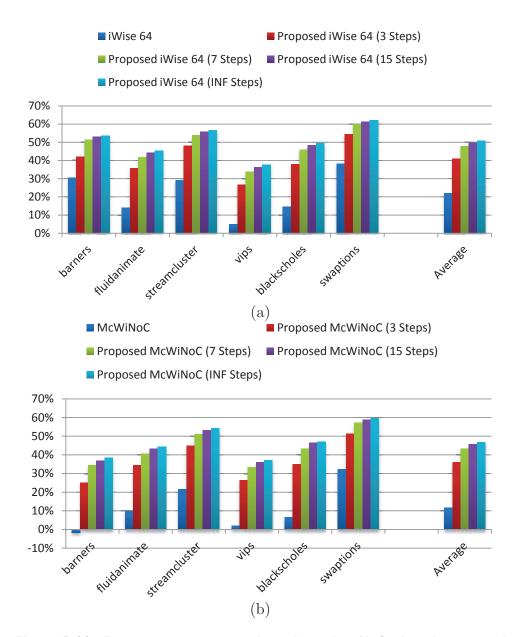

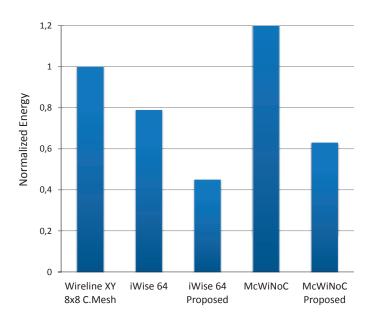

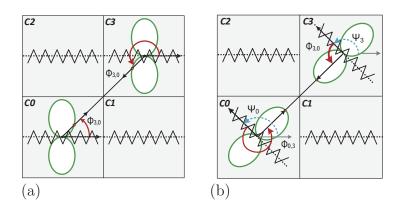

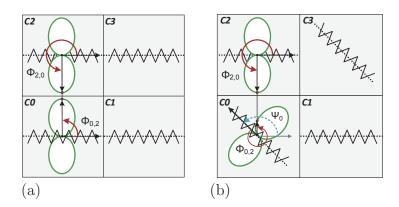

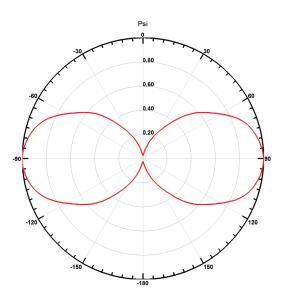

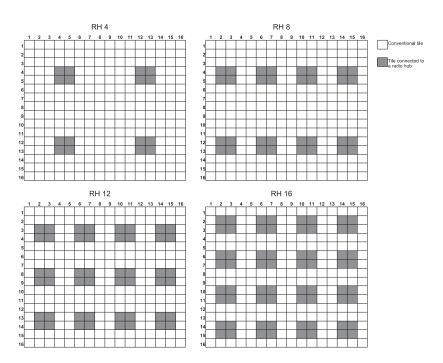

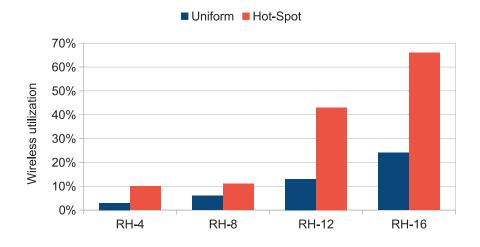

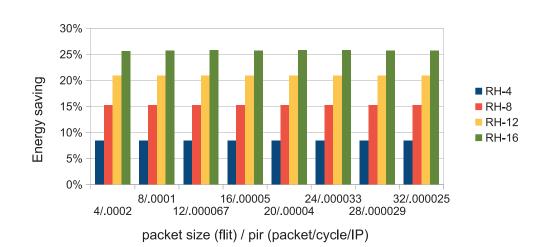

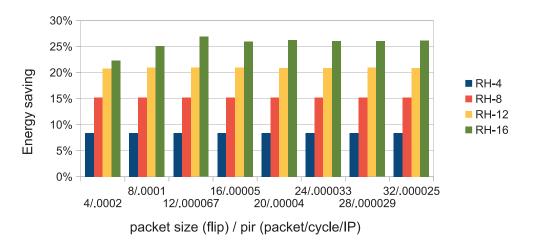

- 5. 2SWL+2SWXBAR+BI [Fig. 3.5(e)]: Like the 2SWL+2SWXBAR in which the data encoding Bus Invert [87] is used. The Encoder and decoder are situated within the network interfaces as proposed in [72].